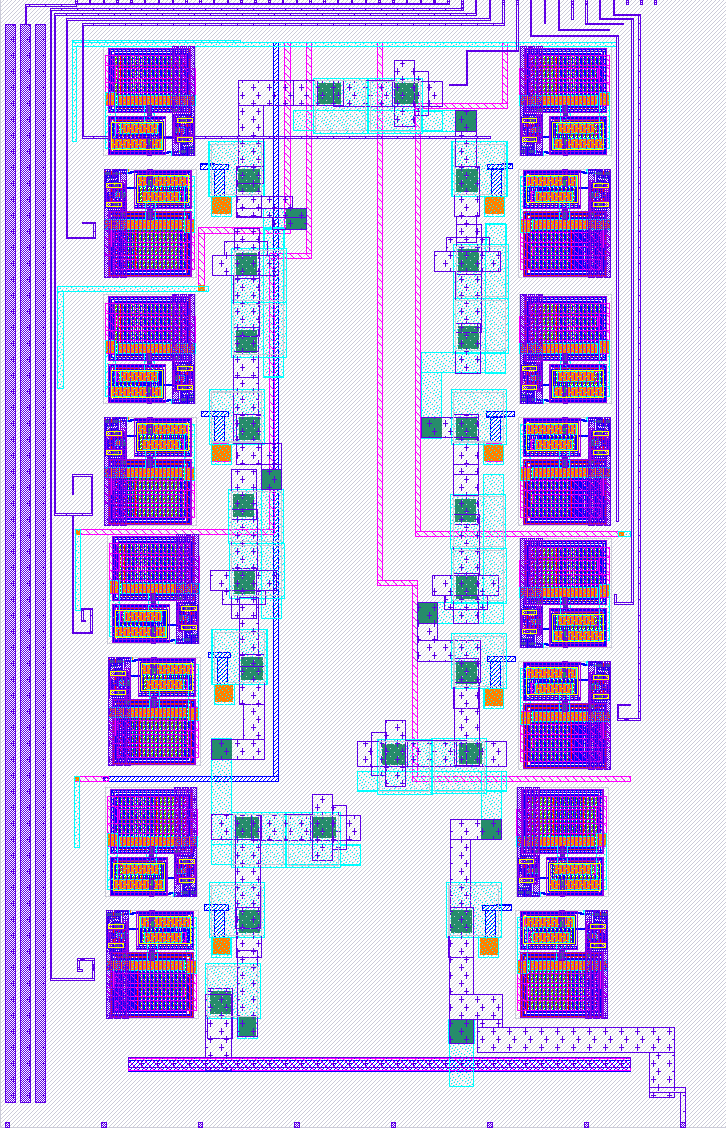

233 Noise test for a CDAC capacitor chain

233 : Noise test for a CDAC capacitor chain

- Author: Venkadesh Eswaranandam & Allan Huang

- Description: This project was made to answer the question of ow much does bad layout affect performance of a SAR ADC

- GitHub repository

- Open in 3D viewer

- Clock: 0 Hz

How to test

This is a test of a C2C array of MIM capacitors to determine how suceptible they are to noise. Clock the digital pins to see what areas are most suceptible to noise. This layout was done intentionaly bad to determine as to what degree layout matters.

External hardware

No external hardware used.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | DAC bit 0 | ||

| 1 | DAC bit 1 | ||

| 2 | DAC bit 2 | ||

| 3 | DAC bit 3 | ||

| 4 | DAC bit 4 | ||

| 5 | DAC bit 5 | ||

| 6 | DAC bit 6 | ||

| 7 | DAC bit 7 |

Analog pins

ua | PCB Pin | Internal index | Description |

|---|---|---|---|

| 0 | A5 | 5 | Analog output |