168 Micro tile container

168 : Micro tile container

- Author: Arna

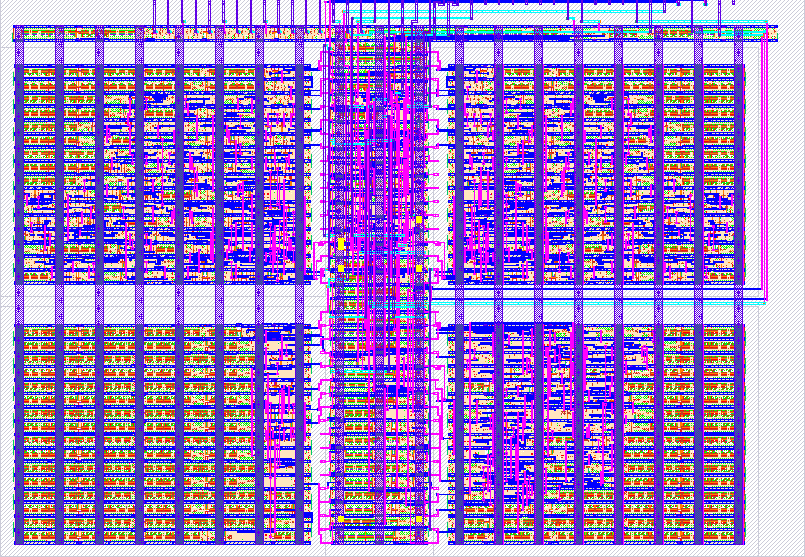

- Description: Example Experimental microtile TDC container

- GitHub repository

- Open in 3D viewer

- Clock: 20000000 Hz

How it works

Four micro tiles were combined into a single Tiny Tapeout tile to analyze power coupling within the Power Distribution Network.

Selecting the active project

Use uio[1:0] to see the output of the micro-tile projects.

Project 1 - Sensor

- Repo:https://github.com/Secure-Embedded-Systems/tt09-microtile-sensor-example

- Author: Arna Roy

- Description: A sensor

How it works

The project generates a delayed clock signal utilizing eight distinct delay lines

How to test

Nothing to test here.

Project 2 - Time to Delay Converters (TDC)

- Repo:https://github.com/Secure-Embedded-Systems/tt09-microtile-tdc-example

- Author: Arna Roy

- Description:Delay line based TDC to measure timing effects

How it works

A Time-to-Digital Converter (TDC) is embedded in one tile and interfaced with the sensor. It measures the time interval between the clock signal from the sensor and the delayed clock signal generated by the sensor.

How to test

Nothing to test here, an experimental basis.

Project 3 - Ring Oscillator (RO)

- Repo:https://github.com/Secure-Embedded-Systems/tt09-microtile-RO-tile1

- Author: Arna Roy

- Description: 32 ROs in one tile to add power stress

How it works

It includes an activation signal capable of enabling 16 ring oscillators simultaneously, primarily to induce power stress for monitoring the Power Distribution Network (PDN)."

Project 4 - Ring Oscillator (RO)

- Repo: https://github.com/Secure-Embedded-Systems/tt09-microtile-RO-tile2

- Author: Arna Roy

- Description: 32 ROs in one tile to add power stress

How it works

Same as the previous design of ROs, just placed in another tile to add power stress

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | in[0] | out[0] | sel[0] |

| 1 | in[1] | out[1] | sel[1] |

| 2 | in[2] | out[2] | |

| 3 | in[3] | out[3] | |

| 4 | in[4] | out[4] | |

| 5 | in[5] | out[5] | |

| 6 | in[6] | out[6] | |

| 7 | in[7] | out[7] |