196 4-bit Multiplier

196 : 4-bit Multiplier

- Author: Jeremy Kang, Idris Al-Wazani

- Description: 4x4 Multiplier using structural verilog

- GitHub repository

- Open in 3D viewer

- Clock: 0 Hz

How it works

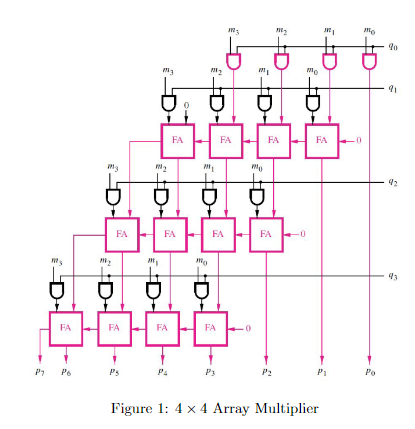

4x4 multiplier using structural verilog. The structure of the 4x4 multiplier array that the exercise should emulate is shown below in the diagram. This multiplies two 4-bit inputs, ‘m’ and ‘q’ in this case, to an 8-bit product, ‘p’. The code takes each consecutive bit of q and cascades it along the first bit of m. From there, full adders are used to combine each bit's value.

How to test

Test cases for inputs m and q should result in the expected product value of p. The test cases in the test python compilation essentially declare two values that should be multiplied and the predicted correct output of the multiplication. To test the functionality, access the test/README.md file.

External hardware

N/A

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | q[0] | p[0] | |

| 1 | q[1] | p[1] | |

| 2 | q[2] | p[2] | |

| 3 | q[3] | p[3] | |

| 4 | m[0] | p[4] | |

| 5 | m[1] | p[5] | |

| 6 | m[2] | p[6] | |

| 7 | m[3] | p[7] |