648 Basic Oszilloscope and Signal Generator

648 : Basic Oszilloscope and Signal Generator

- Author: Pascal Gesell

- Description: Basic oscilloscope & signal generator on an ASIC

- GitHub repository

- Open in 3D viewer

- Clock: 25000000 Hz

Authors: Pascal Gesell, Dr. Torsten Maehne, Dr. Theo Kluter

How it works

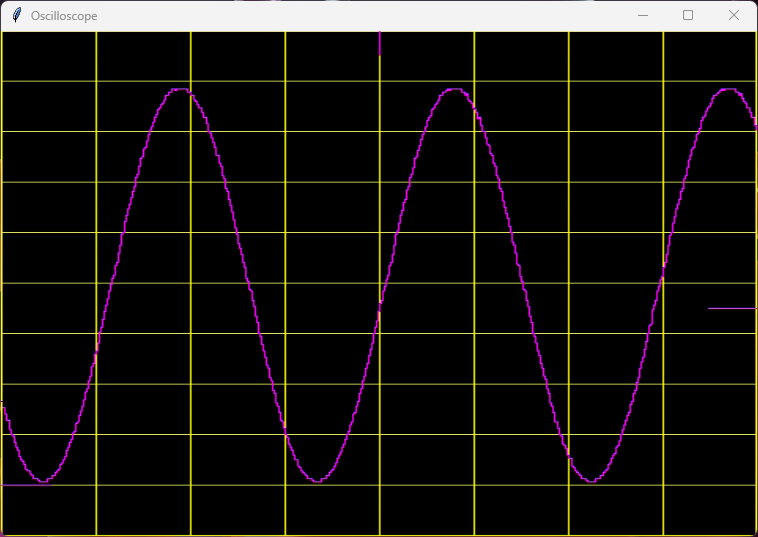

This is a basic oscilloscope design using the experimental VHDL template. It samples the input signal from channel 1 of an ADC Pmod (Digilent PmodAD1) and buffers the samples on an external FRAM. The captured signal is output on screen via a BlackMesa HDMI Pmod. Test signals are generated using Direct Digital Synthesis and are output on channel 1 of the DAC Pmod (Digilent PmodDA2). Four buttons and two switches allow to control the oscilloscope and choose the test signal to generate.

When the trigger button is pressed, a single-shot measurement is taken when the trigger criteria is met. The trigger criteria can be the vertical and horizontal position as well as the trigger level (positive edge or negative edge). The data is buffered onto the external FRAM, with the goal to contain 32k samples before the trigger event and 32k samples after the trigger event. After the data is collected, the data is displayed on the HDMI screen.

Since an external FRAM memory is used with no buffers on the chip, the displayed oscilloscope screen is actually rotated by 90° to the right. Thus only one sample needs to be read from the FRAM per output video line. A Python script is provided for convenience to read the video frames captured by an USB HDMI video grabber, rotate them by 90° to the left and display them on the screen.

The signal generator supports a few basic waveforms: sine, square, triangle and sawtooth. The frequency and amplitude can be adjusted using the buttons and switches. The signal generator is also used to test the trigger functionality and the display of the oscilloscope.

The scope settings are continuously output via UART at 9600 baud (8N1) on uo_out(3).

How to test

Connect the various Pmods to the TinyTapeout 4+ demo board or FPGA board according to the pinout description in the info.yaml file. Connect the output of the DAC to the input of the ADC and connect the HDMI Pmod to a screen or HDMI capture card. Run the trigger to capture a single-shot measurement and display the data on the screen.

External hardware

To test and use this project, you will need the following hardware:

- 1 ⨉ BlackMesaLabs 3-bit HDMI Pmod : A 3-bit HDMI Pmod

- 1 ⨉ Digilent PmodAD1 : A 12-bit ADC Pmod

- 1 ⨉ Digilent PmodDA2 : A 12-bit DAC Pmod

- 1 ⨉ FM25W256G : 32k x 8 FRAM Pmod

- 1 ⨉ Digilent PmodBTN : A 4 Buttons Pmod

- 1 ⨉ Digilent PmodSWT : A 4 Switches Pmod, of which only 2 are used

- Optionally, an HDMI capture card to display the HDMI output on a computer screen

Attention: The above Pmods cannot be directly connected to the TinyTapeout 4+ demo board! The Pmods' pins need to be individually connected to the right Pmod pins of the TinyTapeout 4+ demo board, as documented in the IO section.

FPGA Implementation

The design has been implemented and tested on a Sipeed Tang Nano 9k FPGA board using my own base PCB to have enough available Pmods to test the design.

Acknowledgements

This work was realized under the supervision of Dr. Torsten Maehne and Dr. Theo Kluter as part of my project work in the 5th term of my Bachelor studies of electrical engineering and information technology at Berner Fachhochschule (BFH), Biel/Bienne, Switzerland.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | FRAM MISO | ADC CS | HDMI Pmod Green |

| 1 | Button 1 | DAC MOSI | HDMI Pmod Clock |

| 2 | Button 3 | ADC SCLK | HDMI Pmod HSYNC |

| 3 | Switch 1 | FRAM SCLK | UART_TX Settings Info (9600bps, 8N1) |

| 4 | ADC MISO | DAC CS | HDMI Pmod Red |

| 5 | Button 2 | DAC SCLK | HDMI Pmod Blue |

| 6 | Button 4 | FRAM CS | HDMI Pmod DE |

| 7 | Switch 2 | FRAM MOSI | HDMI Pmod VSYNC |