327 tiny-tapeout-8bit-GPTPrefixCircuit

327 : tiny-tapeout-8bit-GPTPrefixCircuit

- Author: Weihua Xiao

- Description: In this project, we use large language model to automatically create a totally-new prefix network-based high speed adder, for getting a good trade-off between PPA (power performance and area).

- GitHub repository

- Open in 3D viewer

- Clock: 0 Hz

How it works

LLM-aided design of a totally-new 8-bit prefix network-based high speed adder:

{height=45%}

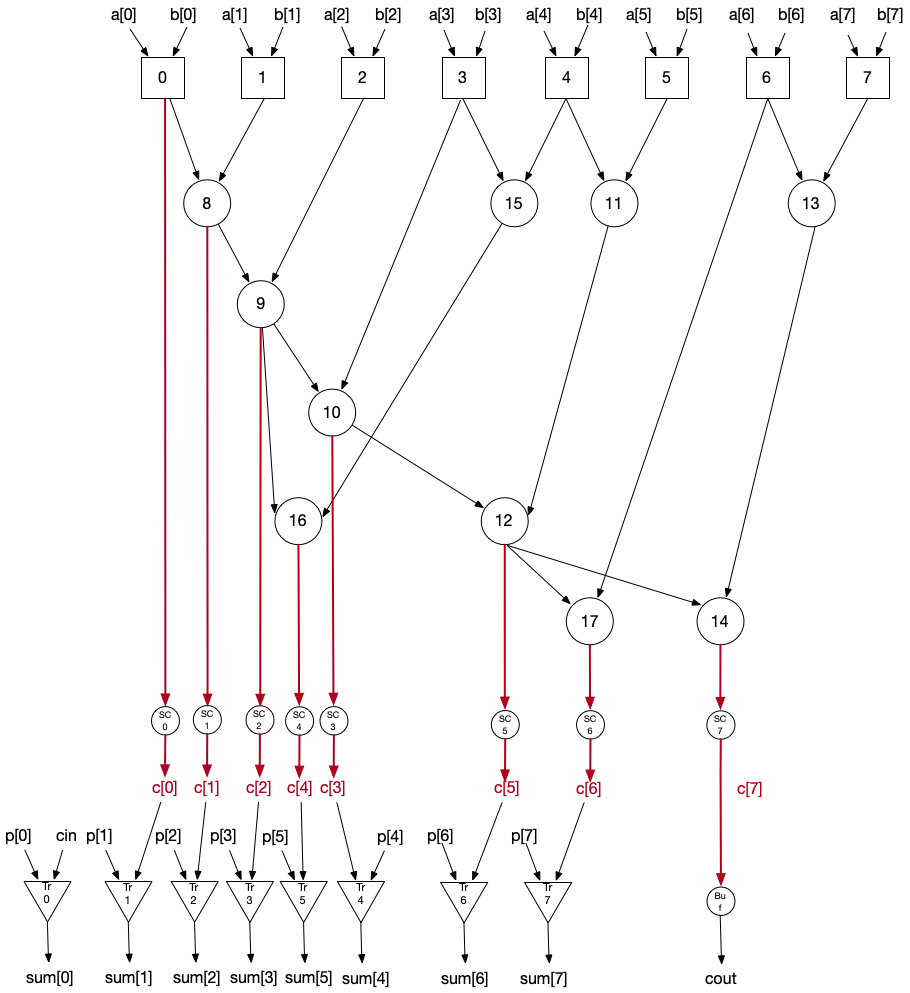

{height=45%}

In this figure, the squares represent the Square module in project.v, the circles represent the BigCircle module in project.v, the small circles represent the SmallCircle in project.v, and the triangles represent the Triangle module in project.v. Each carry signal (c[i]) is generated by circles and each sum signal (sum[i]) is generated by triangles.

How to test

This test systematically applies all combinations of 8-bit values to dut.a and dut.b, verifies the resulting sum dut.sum against the expected 8-bit result ((dut.a + dut.b) & 0xFF), and asserts that the dut behaves correctly.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | a[0] | sum[0] | b[0] |

| 1 | a[1] | sum[1] | b[1] |

| 2 | a[2] | sum[2] | b[2] |

| 3 | a[3] | sum[3] | b[3] |

| 4 | a[4] | sum[4] | b[4] |

| 5 | a[5] | sum[5] | b[5] |

| 6 | a[6] | sum[6] | b[6] |

| 7 | a[7] | sum[7] | b[7] |