234 ECE-UY 2204 4x4 Array Multiplier

234 : ECE-UY 2204 4x4 Array Multiplier

- Author: Jane Manalu, Isabella Menshouse, KJ Moses

- Description: Performs a 4x4 structural array multiplier using fulladder

- GitHub repository

- Open in 3D viewer

- Clock: 0 Hz

How it works

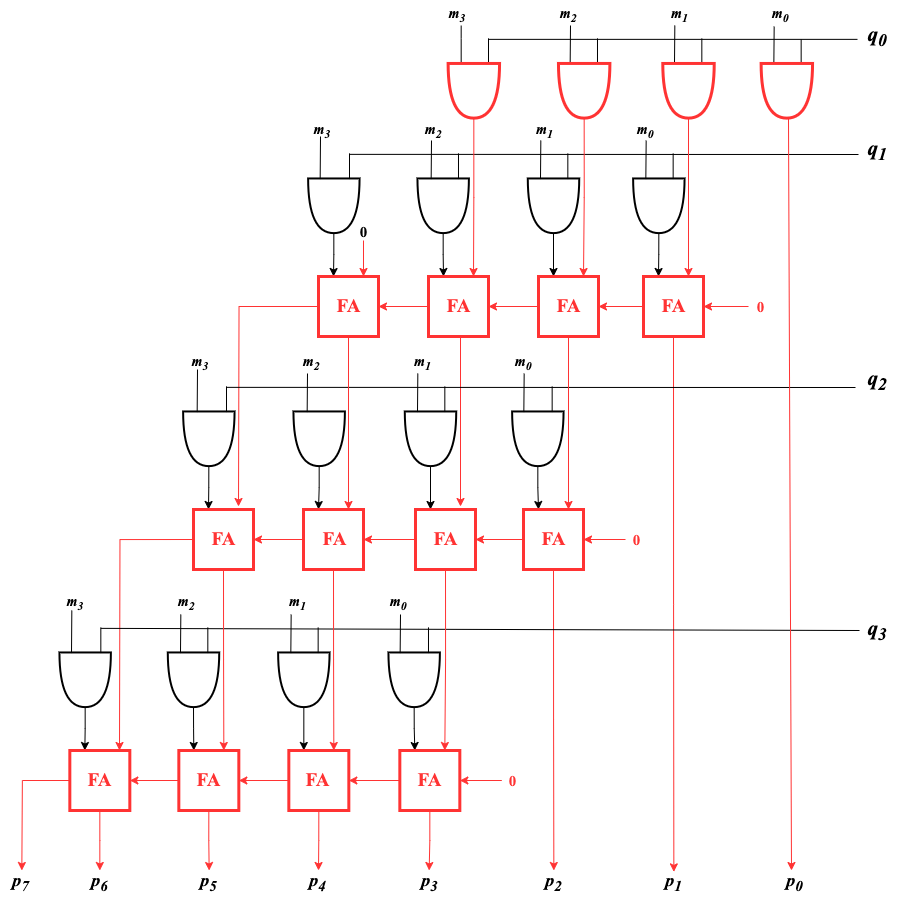

This project will receive two four-bit numbers, where both will be multiplied by the 4x4 array multiplier. The multiplier executes using combinations of full adders (FAs) and two-input AND gates, linked together as shown in the attached circuit diagram. Each row represents partial products generated by the AND gates, where each bit of one number is ANDed with each bit of the other number. The results are then added column by column using full adders, with carries propagated to the next stage. The final outputforms the product of the two four-bit input numbers

How to test

To test this 4x4 array multiplier, provide an 8-bit number, which then will be split into two 4-bit inputs by the multiplier's design source. The circuit will calculate the product, displayed on output. It will compare this output to the expected result to verify the answer. Testing with different 8-bit values will ensure reliable functionality across various inputs.

{height=37%}

{height=37%}

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | q[0] | p[0] | |

| 1 | q[1] | p[1] | |

| 2 | q[2] | p[2] | |

| 3 | q[3] | p[3] | |

| 4 | m[0] | p[4] | |

| 5 | m[1] | p[5] | |

| 6 | m[2] | p[6] | |

| 7 | m[3] | p[7] |