134 8-bit Carry Look-Ahead Adder

134 : 8-bit Carry Look-Ahead Adder

- Author: Seongwan Jeon and Michael Zeng

- Description: Fast 8-bit adder

- GitHub repository

- Open in 3D viewer

- Clock: 0 Hz

How it works

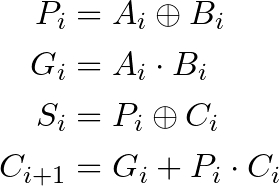

A carry-lookahead adder (CLA) is a type of adder designed for fast speeds. First, it calculates the propagate and generate signals. The propagate signal determines if a carry bit can propagate through to the next bit, and the generate signal bit determines if there is a carry bit. As the name implies, a carry-lookahead adder works by generating a carry bit for every bit in the sum. This works by determining every possible way a carry bit can be generated by combining the generate and propagate signal from previous bits. The equations for the propagate, generate, sum, and carry bit are shown below:

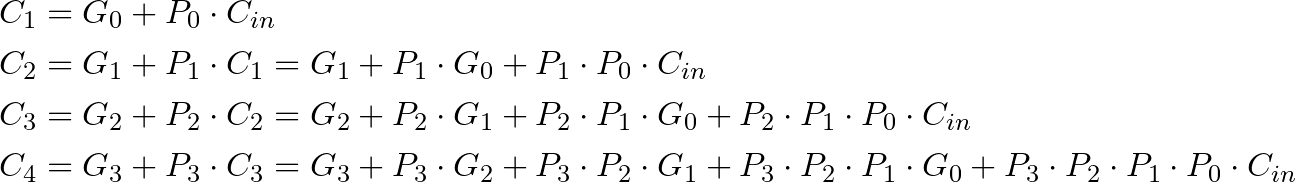

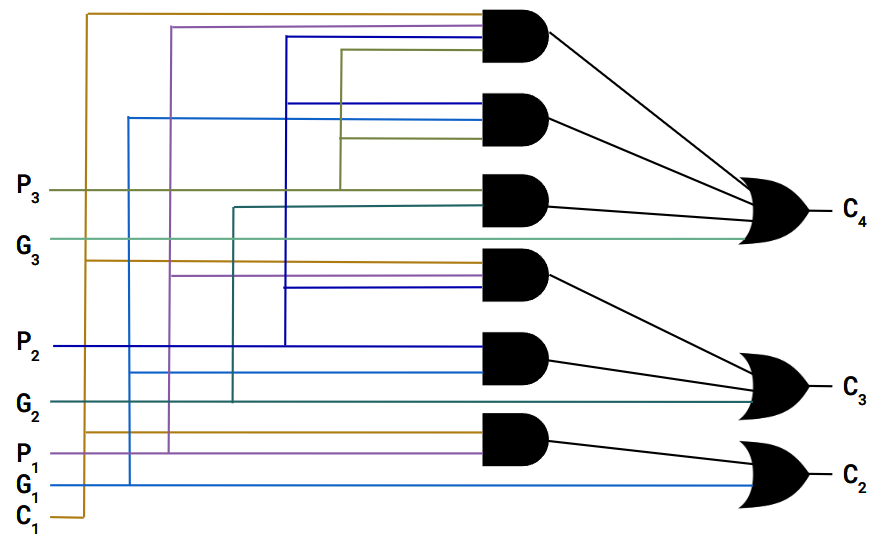

The calculations for the propagate, generate, and sum signals are trivial, but the calculation for the carry bit is dependent on its value in the previous bit, which makes it more complicated to solve. For example, all of the carry bits in a 4-bit CLA adder can be seen in the equation and diagram below:

By calculating the carry bits by using combinatorial logic, a CLA is able to calculate all of the carry bits of the sum without relying on sequential operations, unlike a ripple carry adder. The main time complexity of the ripple carry adder is based on the implementation of the last (and largest) AND gate of the most significant carry bit in the combinatorial equation. This AND gate has n+1 inputs, where n is the bits of the input. The implementation of multiple input AND gates in hardware consists of multiple smaller input AND gates organized in a tree structure, which inherently has a logarithmic time complexity. This logic extends to the CLA which possesses a logarithmic time complexity, and it makes CLAs viewed as one of the fastest implementations of digital adders due to its combinatorial nature. CLAs that calculate large bit-widths can also be designed by using multiple CLAs with smaller bit-widths in parallel to calculate intermediate values. This implementation using a tree structure of adders allows CLAs to also possess a modular design which can be scaled up to handle large bit-widths. However, this tree-like design is an implementation that other parallel prefix adders such as the Kogge-Stone adder utilize to a greater effect. Although CLAs are praised for their speed, it comes at the cost of a large area, as the components needed to calculate the carry bits for larger bit-widths become exponentially larger.

The CLA in this project is an 8-bit adder that does not utilize the implementation using smaller CLAs; rather, it is a fully combinatorial circuit to calculate all 8 bits of the carry signal.

How to test

ui_in[7:0] is addend 1, and uio_in[7:0] is addend 2. ui_out[7:0] is sum.

The adder was tested using all possible pairs of integers from 0 to 255 as inputs, which resulted in 25536 test cases total. For example, the adder would use 0x25 and 0xD7 as inputs, add them up to 0xFC, and the result would be checked to make sure it was the correct output. Carry out was not checked as there is no output pin for a carry out on the board.

External hardware

No external hardware needed.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | a[0] | sum[0] | b[0] |

| 1 | a[1] | sum[1] | b[1] |

| 2 | a[2] | sum[2] | b[2] |

| 3 | a[3] | sum[3] | b[3] |

| 4 | a[4] | sum[4] | b[4] |

| 5 | a[5] | sum[5] | b[5] |

| 6 | a[6] | sum[6] | b[6] |

| 7 | a[7] | sum[7] | b[7] |