403 SSMCl

403 : SSMCl

- Author: Oliver Keszocze

- Description: Slow 3-bit unsigned multiplier

- GitHub repository

- Open in 3D viewer

- Clock: 0 Hz

How it works

This design contains a three-bit multiplier that aims to be area/resource efficient at the expense of using multiple clock cycles to compute the product.

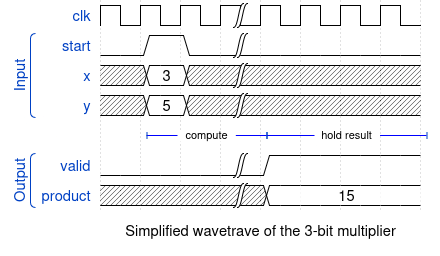

When start is asserted, the values at the x and y inputs are then being streamed into the actual multiplier, taking 3 cycles in total. The multiplier computes the product in 9 cycles and then steams back the 6-bit product in 6 cycles. The result can be seen at the output bit in cycle 18. This is illustrated by the simplified wave trace below.

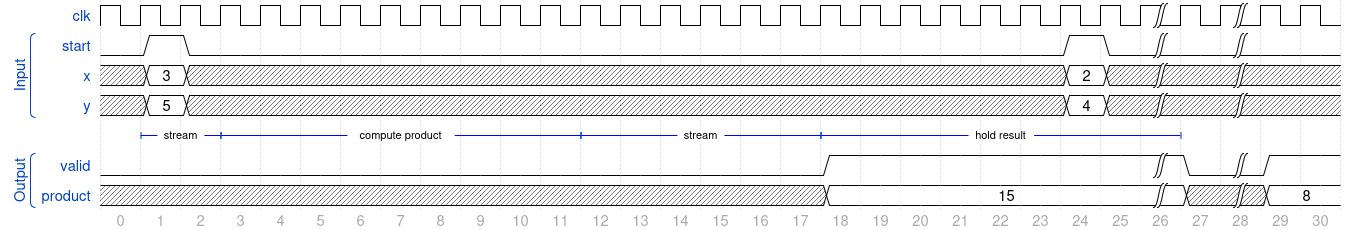

The result will be held until the next multiplication starts streaming back its result (the streaming aspect is fully hidden from the end user in this design!). The following wave trace shows this in full detail (there might be an off-by-one error there; I tend to make those. The general mode of operation is correctly captured by the trace!).

How to test

The input to the multiplier can conveniently be controlled using the web interface of the motherboard. Alternatively, you can connect the input/ouptut pmods as shown in the table in the pinout section below.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | y[0] | product[0] | |

| 1 | y[1] | product[1] | |

| 2 | y[2] | product[2] | |

| 3 | x[0] | product[3] | |

| 4 | x[1] | product[4] | |

| 5 | x[2] | product[5] | |

| 6 | |||

| 7 | start | valid |