494 2-stage Opamp Designs

494 : 2-stage Opamp Designs

- Author: Vipul Sharma

- Description: This project contain opamp circuits designed by participants under SSP training program

- GitHub repository

- Open in 3D viewer

- Clock: 0 Hz

How it works

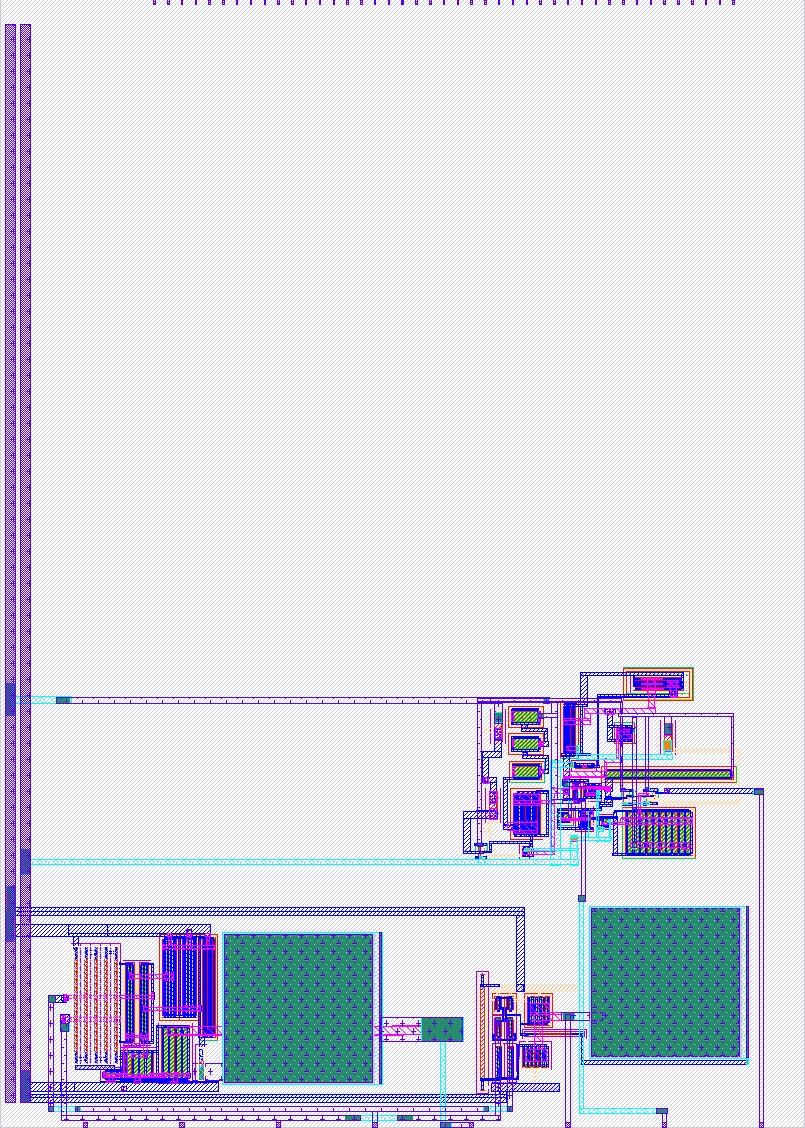

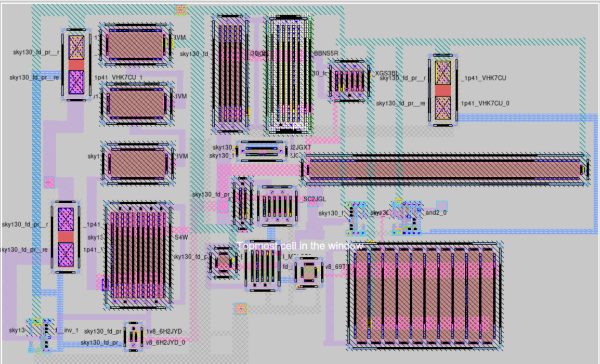

This project contains in total 3 circuits: 2 nos. of 2-stage opamp and 1 POR (Power on reset) circuit. These circuits are designed by participants of analog IC design training conducted by SSP (Saudi Semiconductor Program).

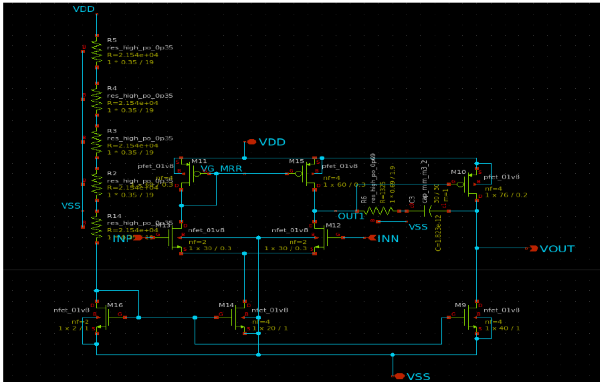

2-stage Opamp

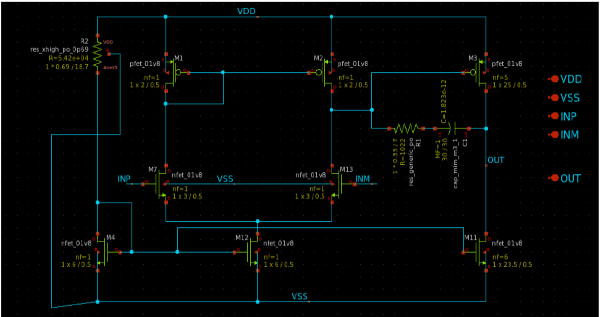

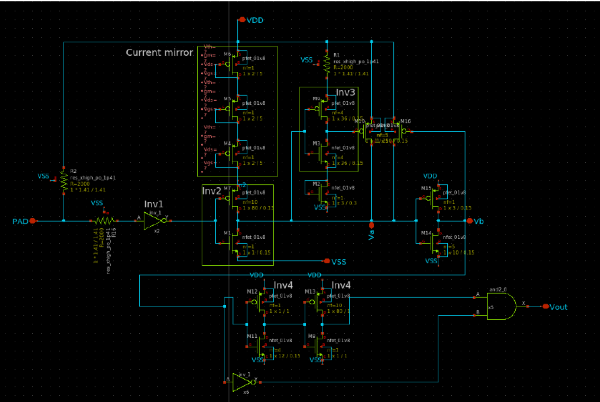

A 2-stage Miller operational amplifier (op-amp) circuit comprises two amplification stages, with a Miller capacitor connected between the output of the first stage and the input of the second stage. This arrangement improves stability and bandwidth, making it ideal for high-gain, high-frequency applications. The 2-stage Miller op-amp is frequently utilized in precision analog signal processing, active filters, and high-impedance buffer circuits.

First Stage: An NMOS differential input pair, selected for its high transconductance and speed, amplifies the difference between the input signals.

Second Stage: A common-source amplifier further increases the gain.

Miller Compensation involves using a capacitor between the output of the first stage and the input of the second stage to stabilize the op-amp by introducing a dominant low-frequency pole, which ensures stability in feedback systems.

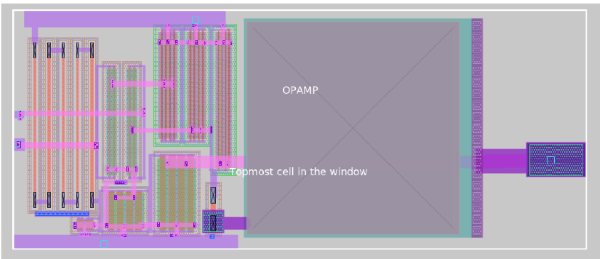

In the op-amp design submissions, Amr Abdelrahman and Majid Sami each presented their designs. The details of their submissions are as follows.

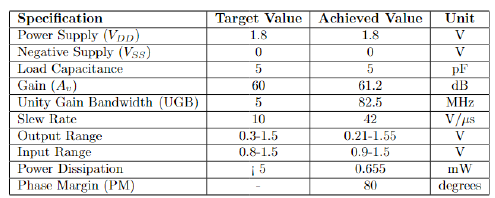

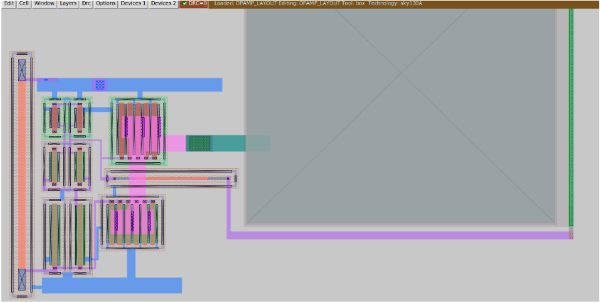

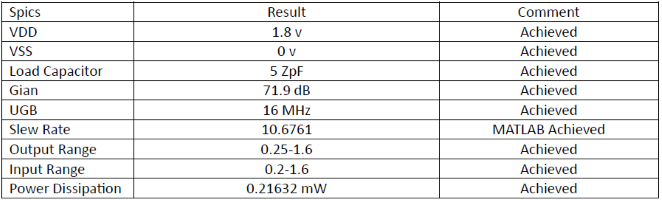

(1) Design by Amr Abdelrahman

(2) Design by Majid Sami

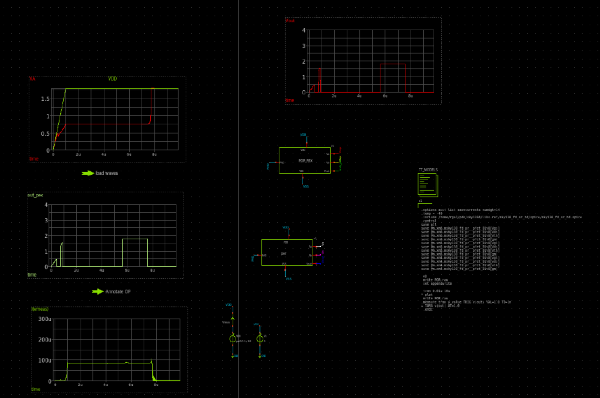

POR (Power On Reset) Circuit

Power-on reset (POR) circuit ensures that electronic systems start up in a known, stable state by generating a reset signal when power is initially applied. This circuit detects when the power supply reaches a sufficient voltage level and holds the reset line active until the voltage stabilizes, preventing erratic behavior and data corruption. POR circuits are crucial in microcontrollers, consumer electronics, and industrial systems, as they guarantee reliable initialization and consistent performance, thereby enhancing system stability and functionality during power-up.The circuit designed without capacitor which yields 30% reduction of chip’s area compared to the conventional designs

(3) Design by Khalid Alorayir

How to test

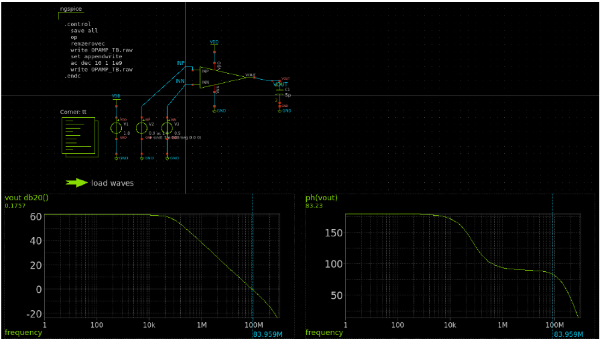

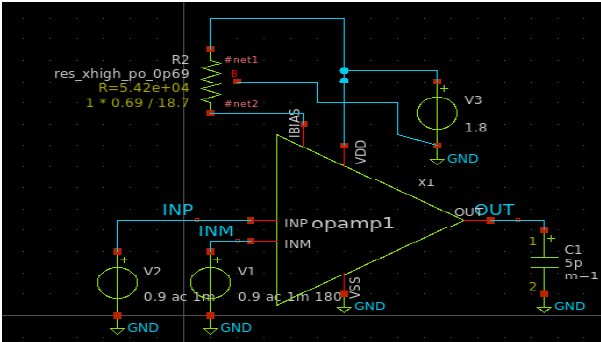

(1) Testing Opamp Circuit

Non-Inverting Configuration

- Set Up the Circuit: Connect the op-amp with the input signal to the non-inverting input (+) and a feedback resistor network to the inverting input (−).

- Power the Op-Amp: Apply the required positive and negative supply voltages.

- Apply Input Signal: Feed a known input signal to the non-inverting input.

- Measure Output: Use an oscilloscope or multimeter to measure the output voltage and verify if Vout = Vin.(1 + Rf/Rin) matches the measured output.

- Check Frequency Response: Ensure consistent gain across frequencies.

- Evaluate Stability and Linearity: Look for any oscillations or instability and confirm the output accurately represents the input signal.

Buffer (Voltage Follower) Configuration

- Set Up the Circuit: Connect the op-amp with output to the inverting input (−) and the input signal to the non-inverting input (+).

- Power the Op-Amp: Apply the necessary supply voltages.

- Apply Input Signal: Feed a known input signal to the non-inverting input.

- Measure Output: Use an oscilloscope or multimeter to measure the output voltage and ensure it closely follows the input with minimal offset.

- Check Frequency Response and Stability: Confirm fidelity of output across different frequencies and ensure stable output without oscillations.

- Assess Load Driving Capability: Test with various loads to verify effective driving.

(2) Testing POR Circuit

- Power up the circuit such that VDD voltage reaches final 1.8V value from 0V in 1us to 10us seep time.

- Check the reset signal with an oscilloscope to confirm proper activation and deactivation.

- Verify that the voltage reaches the threshold and that the reset signal duration is sufficient, especially for rise times of 1µs to 10µs.

- Test the POR circuit under varying power conditions and ensure correct system initialization post-reset.

- Power down and repeat the test to ensure consistent performance.

External hardware

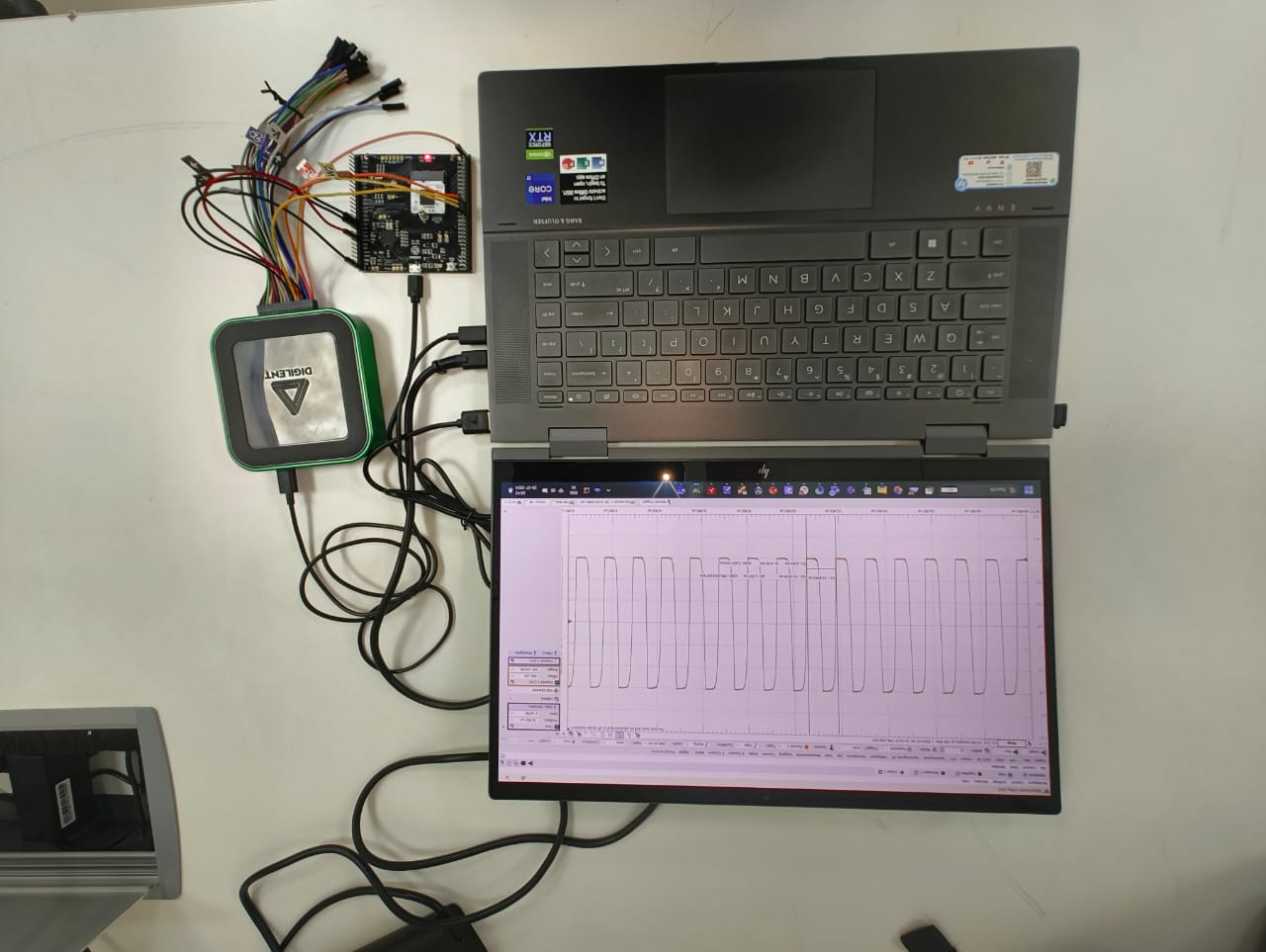

Digilent Analog Discovery can be used for various measurements of opamp circuits.

- Signal Generation: Use the Analog Discovery's waveform generator to create test signals for the op-amp and power-on-reset circuits.

- Measurement: Connect the oscilloscope probes to monitor the input and output signals of the op-amp and observe the behavior of the power-on-reset circuit.

- Frequency Response: Analyze the frequency response of the op-amp by sweeping through various frequencies and recording the output using the Analog Discovery's built-in tools.

- Transient Analysis: Measure how the op-amp and power-on-reset circuits respond to transient signals or sudden changes, such as power-up events.

- Voltage Levels: Check the stability and correct operation of the power-on-reset circuit by measuring the voltage levels and timing of the reset pulse.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | |||

| 1 | |||

| 2 | |||

| 3 | |||

| 4 | |||

| 5 | |||

| 6 | |||

| 7 |

Analog pins

ua | PCB Pin | Internal index | Description |

|---|---|---|---|

| 0 | A5 | 5 | Vout_POR |

| 1 | A0 | 0 | Va_POR |

| 2 | A4 | 4 | OUT_Maj |

| 3 | A1 | 1 | OUT_Amr |

| 4 | A3 | 3 | INN |

| 5 | A2 | 2 | INP |