Tiny Tapeout > Tiny Tapeout Chips > Tiny Tapeout 8 > 329 TT08 - experiments with latch-based shift registers

329 TT08 - experiments with latch-based shift registers

329 : TT08 - experiments with latch-based shift registers

- Author: Ciro Cattuto

- Description: A 512-bit latch-based shift register in 1 tile

- GitHub repository

- Clock: 0 Hz

How it works

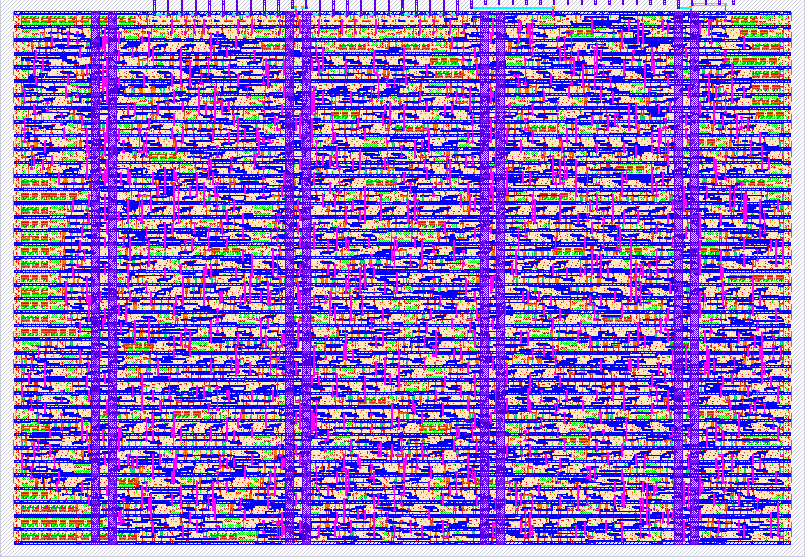

This is an experiment. A 512-bit shift register (SR) implemented using D latches rather than D flip flops. The shift logic relies on a single pulse rippling along the shift register, from the output latch towards the input latch. The SR has one input, one output, and an edge-triggered control signal that controls the shift update. The SR shifts on either a rising or a falling edge of the control signal.

How to test

Shift zeros into the SR until it contains all zeros. Then shift in any sequence of 1s and 0s and observe it appear on the output of the SR after 512 transitions of the control signal.

External hardware

No external hardware required.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | shift register input | shift register output | |

| 1 | shift control (edge-triggered) | ||

| 2 | |||

| 3 | |||

| 4 | |||

| 5 | |||

| 6 | |||

| 7 |