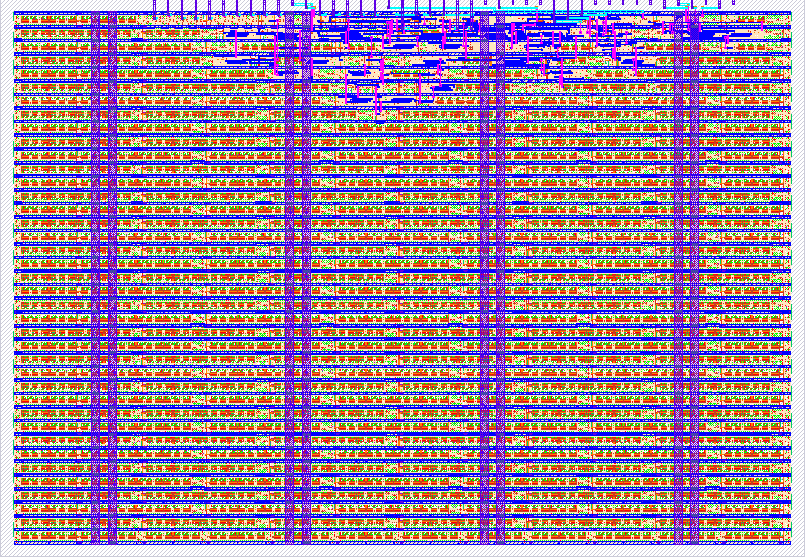

555 Multiple digital design structures

555 : Multiple digital design structures

- Author: A Ghani -Emirates Chips Competence- Design 2

- Description: This design includes multiple digital designs such as positive and negative edge trigger circuits, an LFSR and spike counter and output trigger circuits

- GitHub repository

- Open in 3D viewer

- View in Wokwi

- Clock: 50 Hz

How it works

There are multiple digital designs provided. The first one at the top is a four bit counter, which counts up to 1111 and triggers an output.

The second design includes a +ve and -ve edge trigger logic.

The third design is an LFSR for pseudo random number generator sequence.

The last design has multiple pulse counters and trigger circuit, considered as a reservoir.

How to test

On-chip clock and external inputs could be connected and output ports are used to observe teh output.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | IN0 | OUT0 | D0 |

| 1 | IN1 | OUT1 | D1 |

| 2 | IN2 | OUT2 | D2 |

| 3 | RST_N | OUT3 | D3 |

| 4 | OUT4 | D4 | |

| 5 | OUT5 | D5 | |

| 6 | OUT6 | D6 | |

| 7 | D7 |