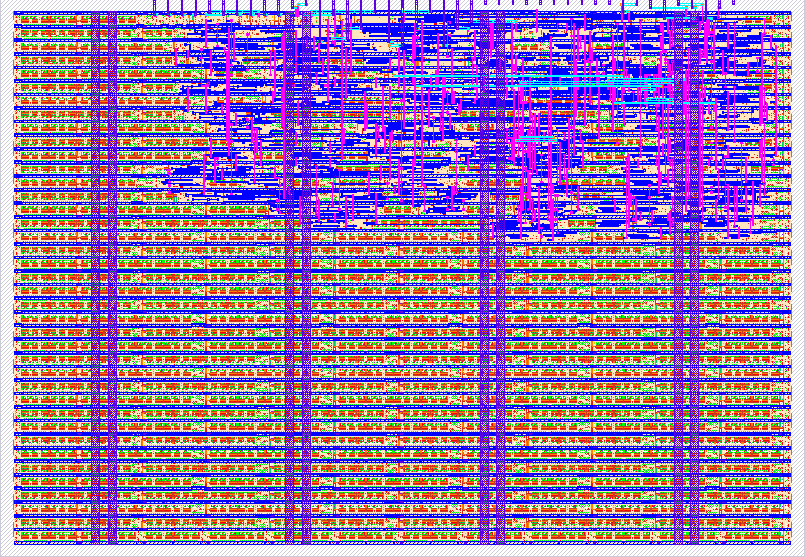

996 Asynchronous FIFO

996 : Asynchronous FIFO

- Author: Priyadharshan, Eshaanjana, Krishnashree, Vignesh

- Description: write(input) and read(output) data at different clocks(wclk & rclk)

- GitHub repository

- Open in 3D viewer

- Clock: 50000000 Hz

How it works

The asynchronous FIFO is a memory buffer that allows safe data transfer between two subsystems operating on different clock domains. It uses separate read and write pointers, which are converted to Gray code for synchronization across domains. Full and empty conditions are detected by comparing synchronized pointers, ensuring reliable communication without metastability issues.

How to test

To test the FIFO, apply write operations with random or sequential data at the write clock domain while simultaneously reading from the read clock domain. Observe that the read data matches the written data in order, with no corruption. Simulation can be run in tools like Vivado, using different clock frequencies for read and write sides to verify asynchronous operation.

External hardware

No external hardware is required. The FIFO can be fully simulated. However, if tested on an FPGA, LEDs or UART modules may be connected to display write/read status, data values, or FIFO full/empty flags.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | wdata[0] | rdata[0] | wclk |

| 1 | wdata[1] | rdata[1] | rclk |

| 2 | wdata[2] | rdata[2] | |

| 3 | wdata[3] | rdata[3] | |

| 4 | winc | full | |

| 5 | rinc | empty | |

| 6 | |||

| 7 |