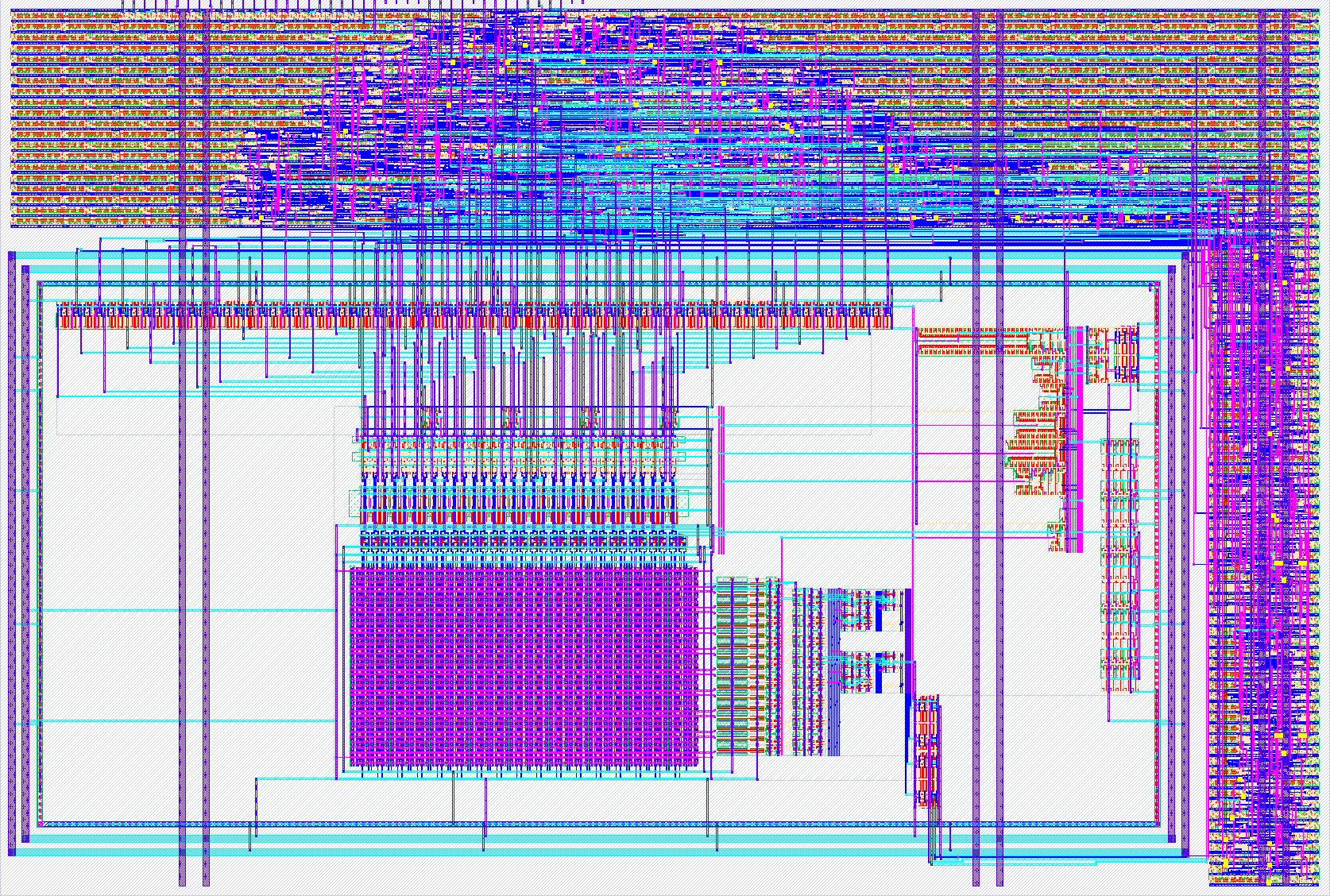

454 Single Port OpenRAM Testchip

454 : Single Port OpenRAM Testchip

- Author: Jesse Cirimelli-Low

- Description: Testchip of single port SRAM macro using two phase clocking

- GitHub repository

- Open in 3D viewer

- Clock: 250000000 Hz

How it works

A simple design with a 16x32 OpenRAM generated 1rw macro using two phased clocking to avoid potential hold violations.

Supports clocks up to 250Mhz

How to test

assign web = ui_in[6]; //

assign csb = ui_in[5]; // chip select

assign sclkb = ui_in[4]; // phased clock b

assign sclka = ui_in[3]; // phased clock a

assign scan_mode = ui_in[2]; //1 scan reg chain, 0 scan phase chain

assign scan_enable = ui_in[1]; //scan chain enable

assign scan_in = ui_in[0]; //input value

uio_in[3:0] are for byte write masking

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | scan_in | scan_reg[0] | wmask[0] |

| 1 | scan_enable | scan_reg[SCAN_WIDTH-1] | wmask[1] |

| 2 | scan_mode | wmask[2] | |

| 3 | sclka | wmask[3] | |

| 4 | sclkb | ||

| 5 | csb | ||

| 6 | web | ||

| 7 | spare_wen |