How it works

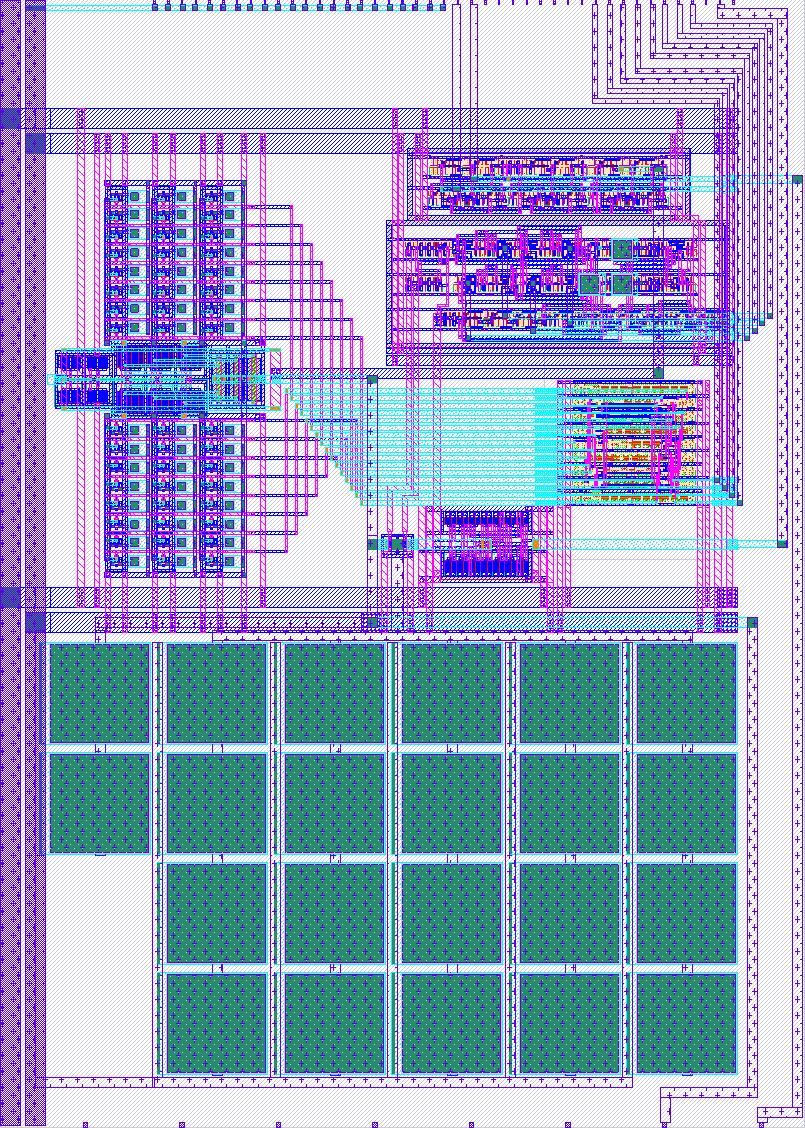

The design is a 2.4 GHz integer-N PLL with a divide by 100 circuit at the output, resulting frequency range of 19.2 - 25.2 MHz. For the reference frequency, internal clock pin is used and it must be set to 20 MHz. The integer divider factor can be controlled by 4-bit digital input (CON_S0 ~ CON_S3). To overcome process variation, the VCO is equipped by discrete control that can be controlled by 4-bit digital input (CON_D0 ~ CON_D3). The output can be observed from an analog pin (FOUT) and two digital pins (DFOUT_HF, DOUT_LF) while another analog pin (VCON) is connected to the control voltage of the VCO.