19 AdEx Neuron NCS

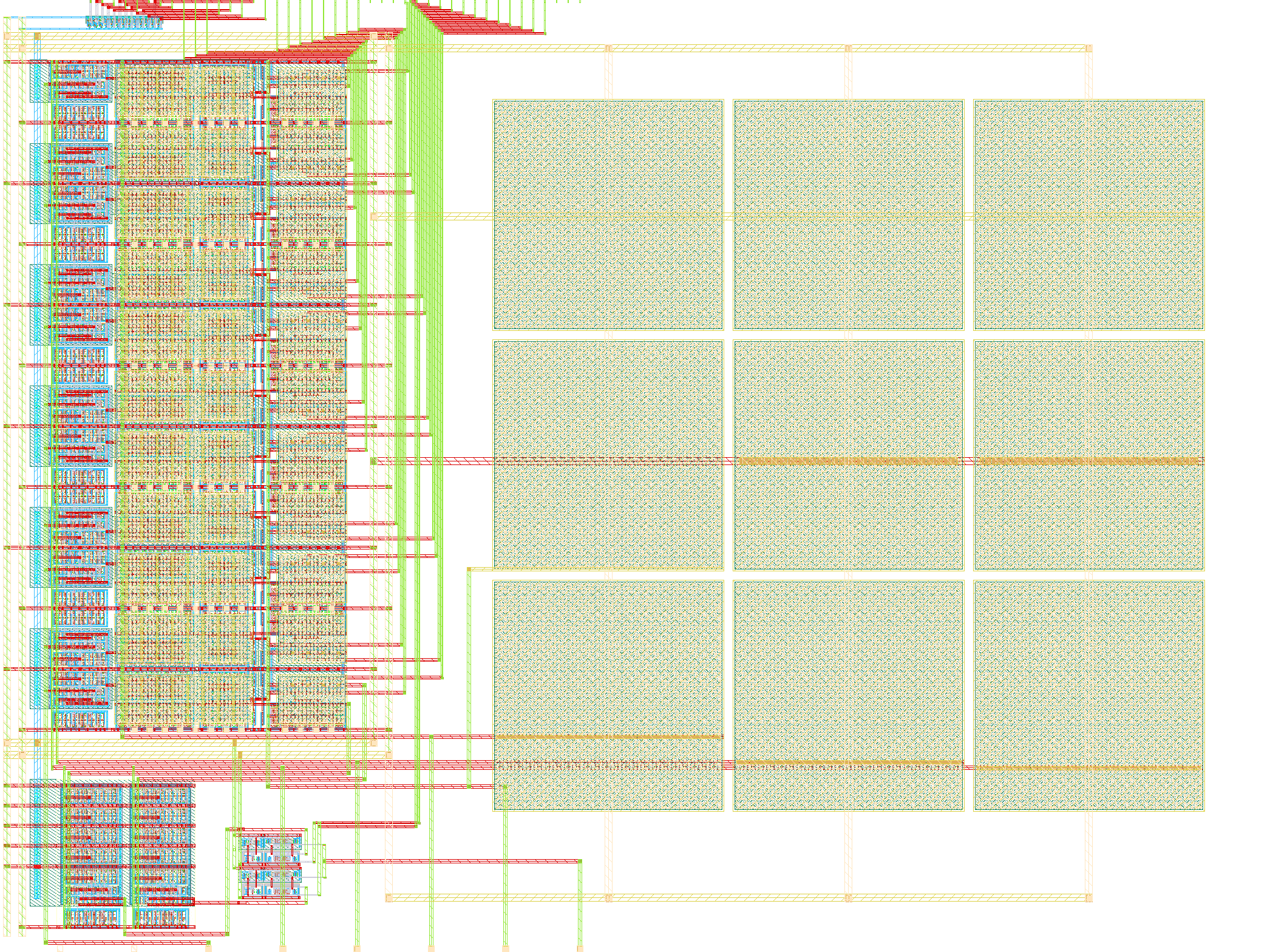

19 : AdEx Neuron NCS

- Author: Chenxi Wen

- Description: Adaptive Exponential Integrate-and-Fire Neuron made using DPI circuits in subthreshold regime

- GitHub repository

- Open in 3D viewer

- Clock: 0 Hz

How it works

This is a DPi circuit based Mixed Signal Adaptive Exponential Neuron.

How to test

This neuron is controlled by analog biases controlled by an SPI register.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | NN_ack_VABI[0] | NN_req_VABO[0] | MUX_sel0_VSI |

| 1 | NN_ack_VABI[1] | NN_req_VABO[1] | MUX_sel1_VSI |

| 2 | NN_ack_VABI[2] | NN_req_VABO[2] | NN_ack_VABI[8] |

| 3 | NN_ack_VABI[3] | NN_req_VABO[3] | NN_ack_VABI[9] |

| 4 | NN_ack_VABI[4] | NN_req_VABO[4] | NN_ack_VABI[10] |

| 5 | NN_ack_VABI[5] | NN_req_VABO[5] | NN_req_VABO[8] |

| 6 | NN_ack_VABI[6] | NN_req_VABO[6] | NN_req_VABO[9] |

| 7 | NN_ack_VABI[7] | NN_req_VABO[7] | NN_req_VABO[10] |

Analog pins

ua | PCB Pin | Internal index | Description |

|---|---|---|---|

| 0 | B7 | 13 | BUF_prob_VX1O |

| 1 | B6 | 12 | NN_ref_VNI |

| 2 | B5 | 11 | NN_tau_VNI |

| 3 | B4 | 10 | V2I_cm_VI |

| 4 | B3 | 9 | V2I_bias_VPI |

| 5 | B2 | 8 | V2I_in_VI |