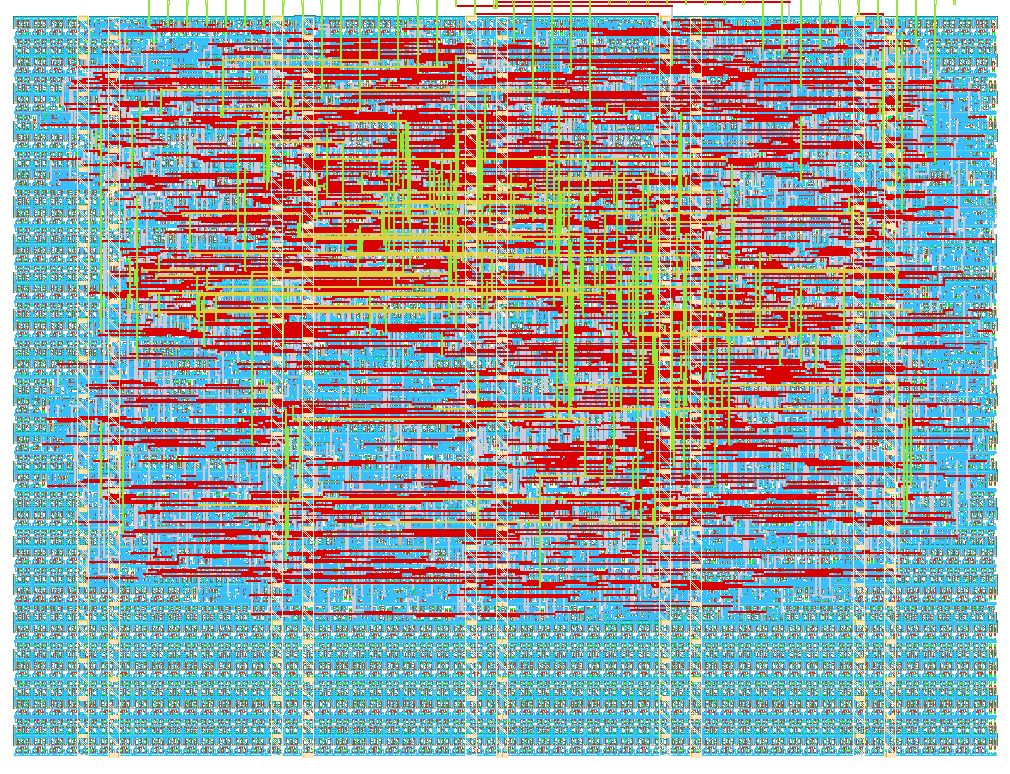

563 smolCPU

563 : smolCPU

- Author: Nicolas Tscherter

- Description: 8 bit custom ISA cpu

- GitHub repository

- Open in 3D viewer

- Clock: 50000000 Hz

How it works

8 bit chip running custom isa. Relying on the RP2008 for Ram emulation.

Registers

The Chip has 8 8-bit gp registers numbered 0 to 7

Registers 0,1 are called accumulator 0,1 in the following.

Register 7 is hardcoded to be used as the source for the page address in paged jumps

The Chip further has a 2 bit flag registers

Set by:

Arithmetic Ops:

F[0] = overflow/borrow

F[1] = carry

bitwise Logic:

F[0] = Zero

F[1] = Parity

shift:

F[0] = Zero

F[1] = Sign

Instruction encoding and semantics

A: The used accumulator RRR: [2:1] The involved Register

Adi: 000I_AIII Acc[A] += IIII

Add 0010_ARRR Acc[A] += Reg[RRR]

Sub 0011_ARRR Acc[A] += Reg[RRR]

Dcd 0100_MMMM Set Flags = 11 if current flag state is in the subset of possible states set([[False,False],[False,True],[True,False],[True,True]]) by the mask MMMM else 0

Cmp 0101_AUGE Let Target = A ? Acc[1] : 0

set flages as follows:

Flag[1] = ((G && A signed grater than Target) || (E && A == Target)) ? 1 : 0

Flag[0] = ((G && A unsiged grater than Target) || (E && A == Target)) ? 1 : 0

note: the U bit is unused

Jmp 0110_PRRR if flag[0]: instruction_pointer = Reg[RRR] if P: Mem[I,255] = Reg[7]

Xor 0111_ARR Acc[A] ^= Reg[RRR]

Ldr 1000_ARRR Acc[A] = Reg[RRR]

Str 1001_ARRR Reg[RRR] = Acc[A]

Ldm 1010_ARRR Acc[A] = Mem[Reg[RRR]]

Stm 1011_ARRR Mem[Reg[RRR]] = Acc[A]

And 1100_ARR Acc[A] &= Reg[RRR]

Or_ 1101_ARR Acc[A] |= Reg[RRR]

Sll 1110_ARR Acc[A] <<= Reg[RRR]

Srl 1111_ARR Acc[A] >>= Reg[RRR]

How to test

Work in progress. Check the project repo for updates.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | data0 | read_en | addr0/data0 |

| 1 | data1 | instr_en | addr1/data1 |

| 2 | data2 | cpu_flag[0] | addr2/data2 |

| 3 | data3 | cpu_flag[1] | addr3/data3 |

| 4 | data4 | addr4/data4 | |

| 5 | data5 | cpu_state[0] | addr5/data5 |

| 6 | data6 | cpu_state[1] | addr6/data6 |

| 7 | data7 | cpu_state[2] | addr7/data7 |