232 8-bit SEM Floating-Point Multiplier

232 : 8-bit SEM Floating-Point Multiplier

- Author: Jordan Delos Reyes

- Description: Custom 8-bit Sign-Exponent-Mantissa floating-point multiplier with NaN and zero handling.

- GitHub repository

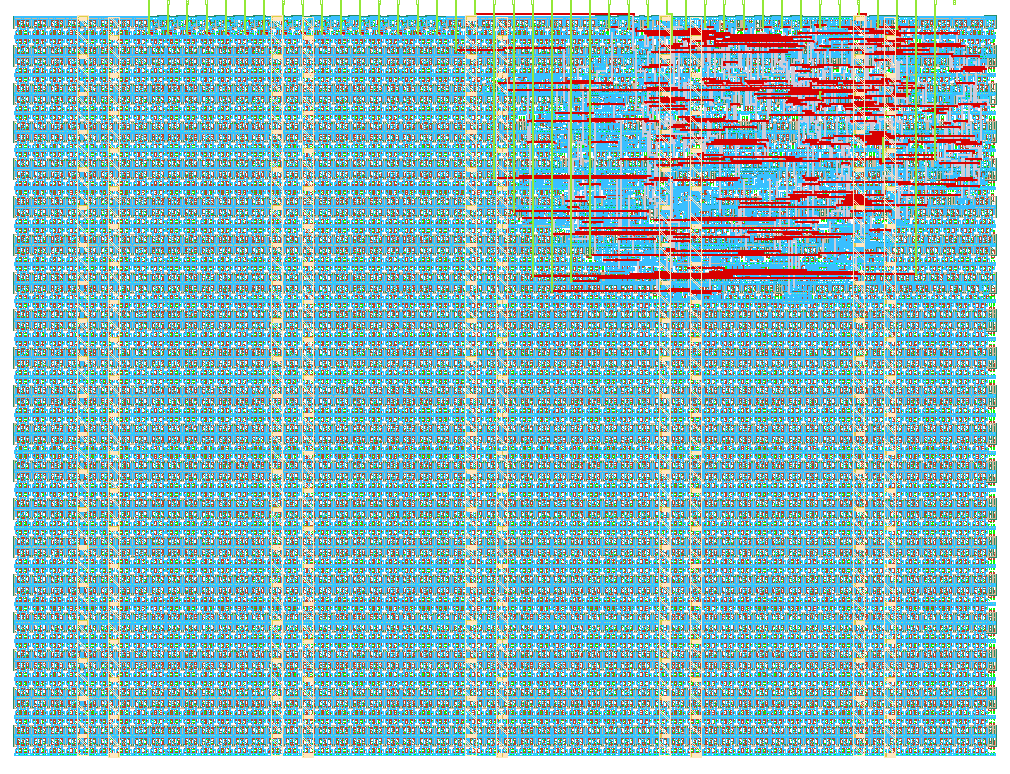

- Open in 3D viewer

- Clock: 50000000 Hz

8-bit SEM Floating-Point Multiplier

What it does

This project implements an 8-bit floating-point multiplier using a custom Sign–Exponent–Mantissa (SEM) format.

Each 8-bit number is structured as:

S EEEE MMM

- 1 sign bit

- 4 exponent bits

- 3 mantissa bits

The design multiplies two SEM numbers and produces an 8-bit SEM result. The architecture is divided into three major blocks:

- Sign computation

- Mantissa multiplication and normalization

- Exponent addition and adjustment

The design also handles two special cases:

-

NaN

If either input equalsS.1111.111, the output is forced to0_1111_111. -

Zero

If either input equalsS.0000.000, the output is forced to0_0000_000.

Priority:

NaN > Zero > Normal multiplication

How to use

Inputs

ui_in[7:0]→ Operand A (SEM format)uio_in[7:0]→ Operand B (SEM format)clk→ Clockrst_n→ Active-low reset

Output

uo_out[7:0]→ Result (SEM format)

Operation

- Apply operands A and B.

- Pulse reset low to initialize the system.

- On the next clock edge, the multiplier produces the result.

The design is fully synchronous and updates on the rising edge of clk.

Example

Input A: 0_0101_010

Input B: 0_0011_001

Output: S_EEEE_MMM (result of SEM multiplication)

If either input is:

x_1111_111 → Output = 0_1111_111 (NaN)

x_0000_000 → Output = 0_0000_000 (Zero)

External hardware

No external hardware is required.

The module is fully self-contained and purely digital.

Design details

The multiplier is implemented using three synchronous submodules:

-

sign

Computes the result sign as the XOR of the input signs. -

mantissa

Multiplies mantissas, normalizes the result, and generates an exponent increment. -

exponent

Adds exponents and applies normalization adjustment.

The final result is registered for synchronous output.

Limitations

- No support for infinities.

- Only a single canonical NaN is supported.

- Exponent overflow behavior depends on internal saturation logic.

Verification

The design was verified through simulation of:

- Normal multiplication cases

- Zero input cases

- NaN input cases

- Sign combinations

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | A_M0 | R_M0 | B_M0 |

| 1 | A_M1 | R_M1 | B_M1 |

| 2 | A_M2 | R_M2 | B_M2 |

| 3 | A_E0 | R_E0 | B_E0 |

| 4 | A_E1 | R_E1 | B_E1 |

| 5 | A_E2 | R_E2 | B_E2 |

| 6 | A_E3 | R_E3 | B_E3 |

| 7 | A_S | R_S | B_S |