Tiny Tapeout > Tiny Tapeout Chips > Tiny Tapeout SKY 25b > 588 VGA Screensaver with Zero to ASIC Logo

588 VGA Screensaver with Zero to ASIC Logo

588 : VGA Screensaver with Zero to ASIC Logo

- Author: Matt Venn, Louis Ledoux

- Description: VGA Zero to ASIC Logo bouncing around the screen meta shaped chip

- GitHub repository

- Open in 3D viewer

- Open in VGA Playground

- Clock: 25175000 Hz

How it works

This design drives a 640×480 VGA output and displays a bouncing “Zero to ASIC” logo. It supports a tiled mode and an animated color gradient. Optionally, a Gamepad Pmod can control motion.

How to test

Connect to a VGA monitor. Set the following inputs to configure the design:

tile(ui_in[0]) to repeat the logo and tile it across the screen,solid_color(ui_in[1]) to use a solid color instead of an animated gradient.

If you have a Gamepad Pmod connected, you can also use the following controls:

- Start button: start/pause bouncing

- Left/right/up/down: change the bouncing direction (if bouncing) or move the logo around the screen (if paused)

External hardware

- Tiny VGA Pmod

- Optional: Gamepad Pmod

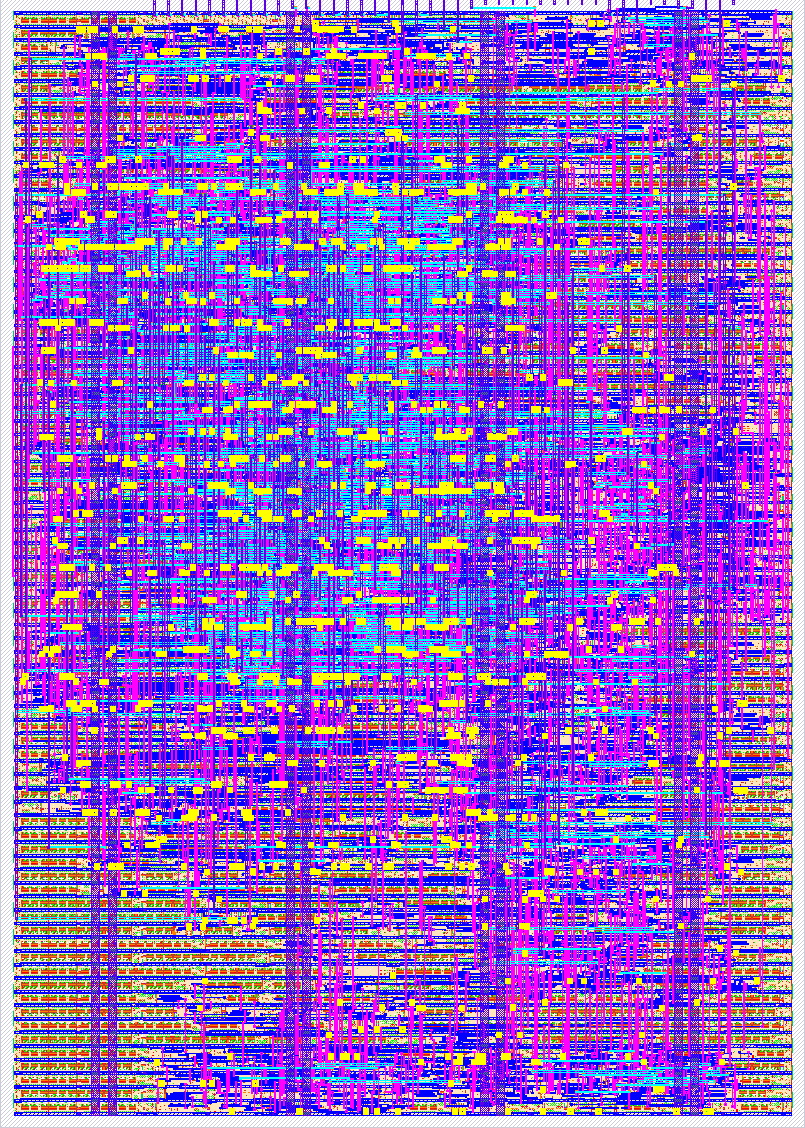

Harden flow with artwork (advanced)

We extend LibreLane’s Classic flow by inserting a custom ODB Python step before global placement. This step can generate placement blockages from a bitmap to “shape” placement density and create chip art.

- Base: LibreLane Classic flow

- Extension: inserts

Odb.ApplyArtjust beforeOpenROAD.GlobalPlacementSkipIO - Implementation: lightweight LibreLane plugin packaged in a small Docker overlay

Quick start

-

Build the custom LibreLane image (adds the plugin + Pillow):

docker build -t my-librelane:mock -f docker/librelane-mock/Dockerfile .

-

Select the image and choose an input image (PNG/JPG):

export LIBRELANE_IMAGE_OVERRIDE=my-librelane:mockexport TT_ART_IMAGE="$PWD/art/zero-to-asic-logo.png"

Optional knobs:

TT_ART_GRID(int, default 40): grid columns; rows follow image aspectTT_ART_THRESHOLD(0..255, default 128): luminance thresholdTT_ART_INVERT(1/true/yes): invert selectionTT_ART_AREA_PCT(0..100, default 20): scale art area within the core

-

Run harden with the art step enabled:

./tt/tt_tool.py --harden --with-art

-

Inspect results:

- Step log:

runs/wokwi/<NN>-odb-applyart/odb-applyart.log - Preview:

runs/wokwi/<NN>-odb-applyart/art_preview.png

- Step log:

Notes:

- If container env vars aren’t forwarded, the tool writes

art_config.jsonin the project root and the step reads it automatically. - The art step fails when no image is provided, to avoid silent fallbacks.

What the step does

- Reads the OpenDB after floorplan

- Rasterizes the input image to a grid

- For selected cells, creates soft placement blockages in the core bounding box (scaled by

TT_ART_AREA_PCT) - Writes the ODB back in-place and saves a small preview image

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | tile | R1 | |

| 1 | solid_color | G1 | |

| 2 | B1 | ||

| 3 | VSync | ||

| 4 | gamepad_latch | R0 | |

| 5 | gamepad_clk | G0 | |

| 6 | gamepad_data | B0 | |

| 7 | HSync |