418 Simon Says

418 : Simon Says

- Author: Noah Hu and Michelle Chen

- Description: Simon Says Game

- GitHub repository

- Open in 3D viewer

- Clock: 10000000 Hz

How it works

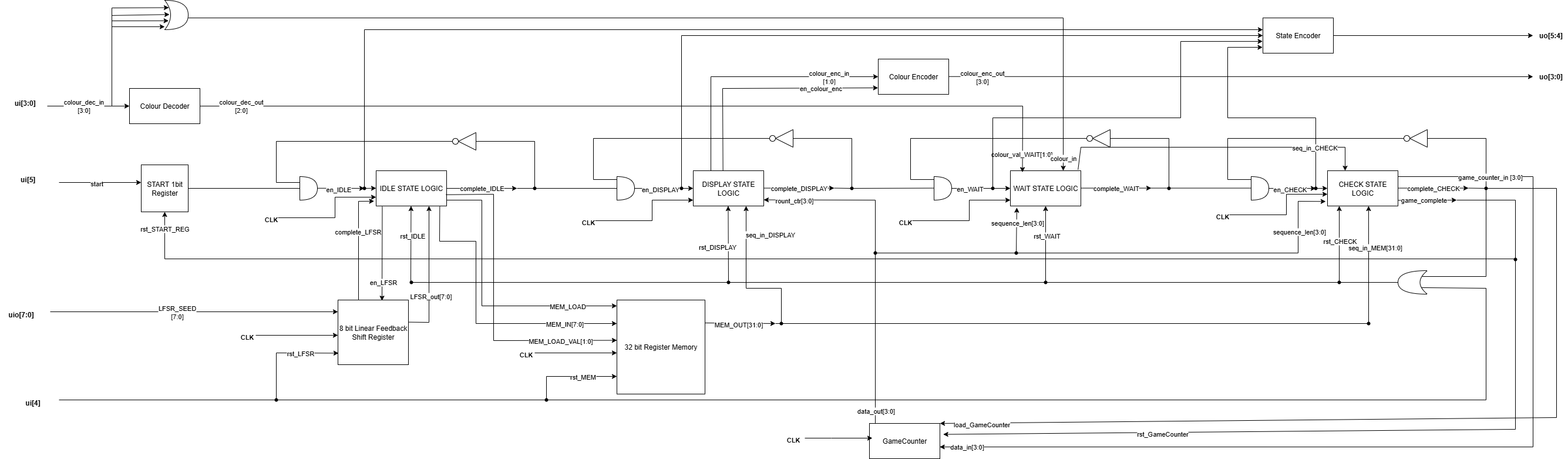

This project implements a modified version of the Simon Says game. The design uses digital logic to control game flow and memory elements to store a pseudo-random sequence of colors. The system interfaces with external buttons and LEDs to allow human interaction and gameplay.

Game Flow

Upon powering up the chip:

-

Idle State

- Waits for the

startsignal. - A 8-bit seed is loaded into the LFSR via the bidirectional bus.

- A 32-bit pseudo-random sequence is generated by the LFSR.

- Each color is encoded in 2 bits, allowing 14 colours (16 × 2 bits = 32 bits - 4 bits (for start and end)).

- The sequence is stored in a 32-bit register-based memory.

- Waits for the

-

Display State

- Displays the 14 colour sequence on the LEDs.

-

Wait State

- Waits for user inputs through button presses and stores the respective 14-colour sequence.

-

Check State

- Verifies the user inputs against the stored colour sequence.

- If correct, the game ends and is considered to be won. The

game_completesignal will be1, indicating a win. - If incorrect, the game ends and is considered to be lost. The

game_completesignal will be0, indicating a loss. - Note: Based on the design even if the user enters an incorrect colour early on, the user must enter enough colours for that sequence before the mistake is detected. For example, if the second colour entry is incorrect, the user will still need to enter the rest of the colours in the 14-colour sequence.

-

End of Game

- Triggered when the player enters their sequence and is checked by the

check_stateblock. The user can press the reset button to begin a new round of Simon Says.

- Triggered when the player enters their sequence and is checked by the

Key Components

- 32-bit Register Memory

- Stores the color sequence (14 values × 2 bits + 4 bits for start and end).

-

8-bit Linear Feedback Shift Register (LFSR)

- Generates a pseudo-random 32-bit sequence.

- Uses a 8th-order primitive polynomial to ensure maximal length (2^8 - 1 = 255 values).

- Special logic ensures the state never becomes all zeros.

- Seeded externally to vary game sequences across resets and sessions.

-

Color Encoder/Decoder

- Converts 4 individual button signals into a single 2-bit color value for logic comparison (and vice versa).

- Ensures consistent color encoding across modules.

-

Game States

- Contains the logic to execute each state of the game.

-

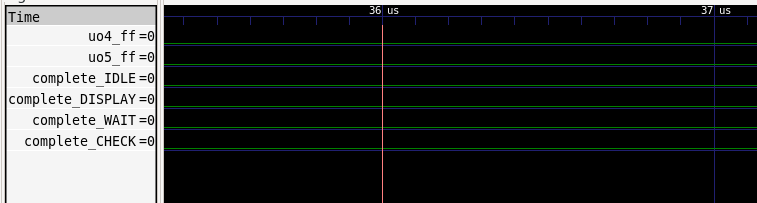

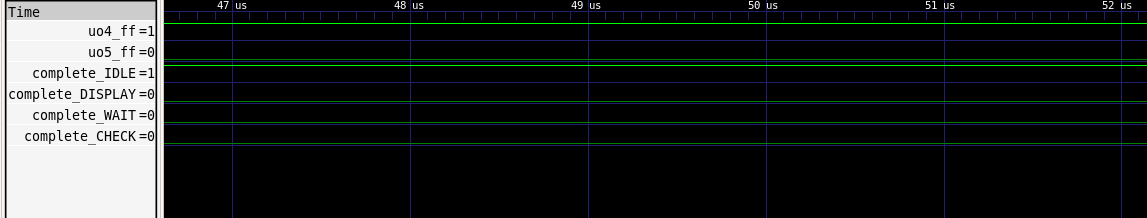

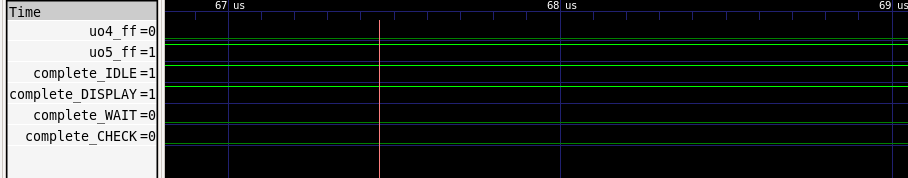

State Debug

- Current game state -- represented as a 2 bit value -- is assert on 2 output ports as a means to debug.

uo_out[5]uo_out[4]

IDLE: 00 DISPLAY: 01 WAIT: 10 CHECK: 11

Block Diagram

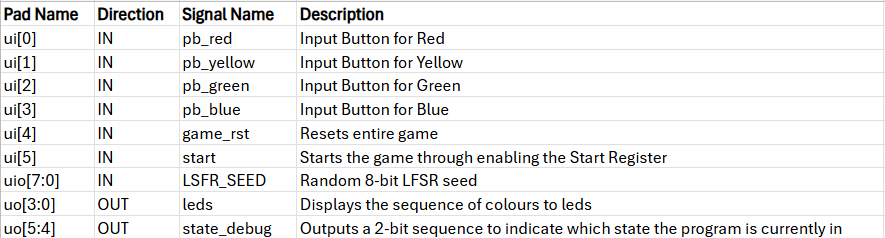

I/O Table

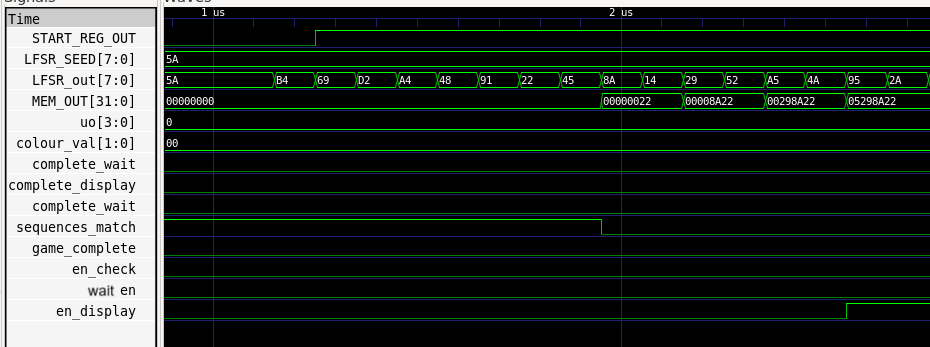

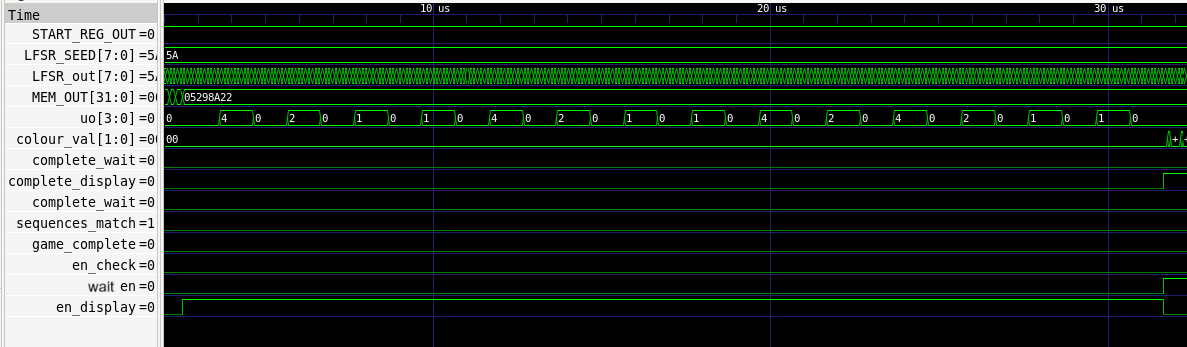

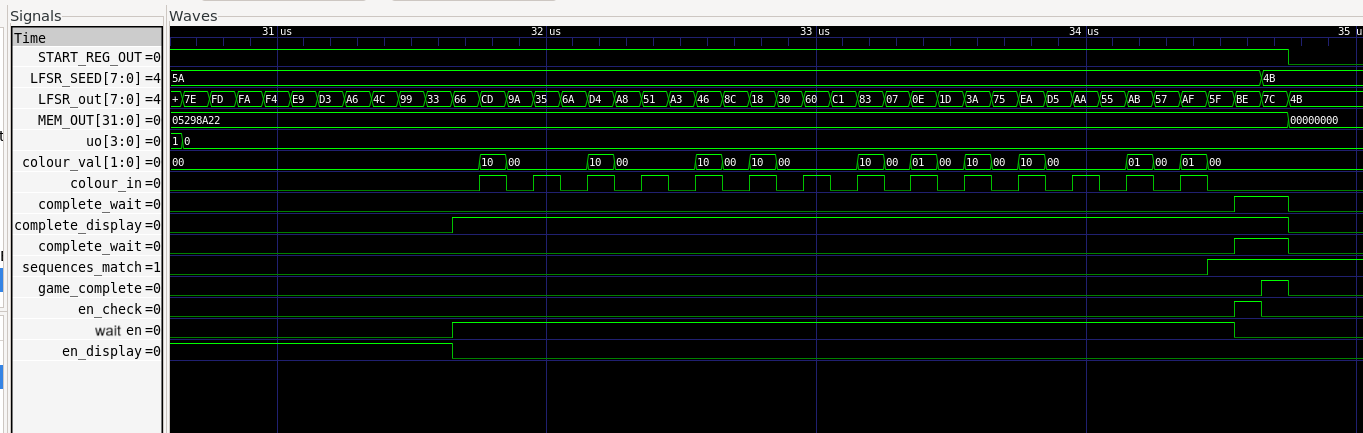

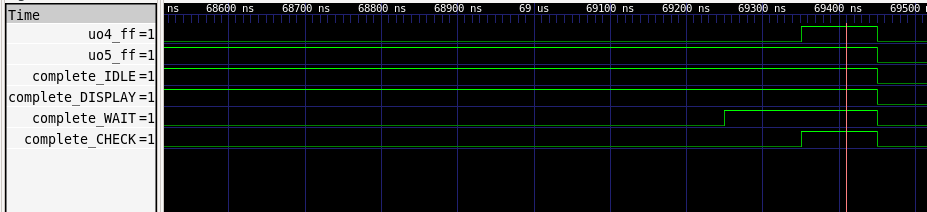

Timing Diagrams

During IDLE state, LFSR takes seed and produces shifted outputs. The outputs are loaded into the 32bit memory 8 bits at a time. See LFSR_SEED, LFSR_out, MEM_OUT signals. <br>

During Display the sequence in memory is decoded and asserts on the output lines. See uo[3:0]. signal. Note, for simulation, the delay between displayed colours is significantly reduced. When played by the user, each colour display holds for 500ms.<br>

During Wait and check, the user inputs are recorded and compared against the generated sequence. In this case, the sequence matches and thus game_complete goes to 1. See colour_val, colour_in signals, sequence_match, and game_complete signals.<br>

How to test

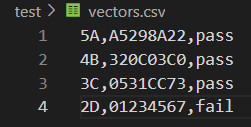

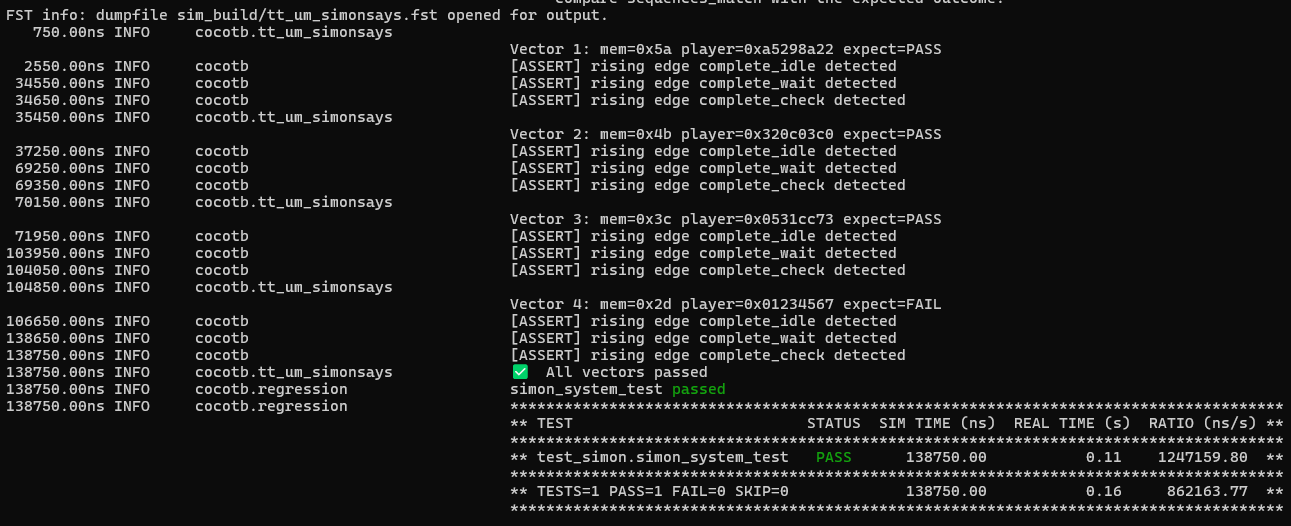

Functional Testing - test_simon.py

This testbench performs a smoke test and a full functional verification of the Simon Says system using stimulus vectors from a CSV file. It exercises the interaction between memory loading, display, wait, and check states, simulating user inputs and verifying the game logic. The test assumes a 10 MHz clock (50 ns half period).

Sequential simulation:

- Resets the system and asserts

START. - Waits for the

IDLEstate to complete before loading the test sequence into memory. - Waits for the system to enter the

WAITstate (en_WAIT). - Replays the player’s input sequence as a series of button presses.

- Waits for completion signals (

complete_WAIT,complete_CHECK). - Compares the result of the sequence check against the expected outcome.

Success criteria:

- The system completes the

WAITandCHECKstates for each test vector. - The

sequences_matchflag correctly reflects whether the player’s sequence matches the stored sequence. - The observed PASS/FAIL result matches the expected outcome from the CSV vector.

Failure criteria:

- Timeout or failure to assert critical handshake signals within the timeout window.

- Mismatch between expected and actual pass/fail results for any test vector.

CSV Contents:

<br>

<br>

| Seed | User Input | Expected Result |

Results:

<br>

<br>

Gameplay Functionality

- Simulate a win by entering the correct sequence.

- Simulate a mistake during the round. Game should detect incorrect input in

CHECKand set thegame_completesignal to 0, indicating a loss.

Game State Transitions

- Verify transitions using state debug signal:

- `IDLE → DISPLAY → WAIT → CHECK

- Confirm each state's role:

DISPLAY: Colour is displayed long enough (500ms) for users to understand and colour sequence is consistent between rounds.WAIT: State ends only when all required colours are entered. (ex. in the 14-colour sequence, must wait until 14 colours are entered).CHECK: Correct validation. (if the user enters a correct sequence, it should end the game and setgame_completeto 1, indicating a win.)

Startup & Seeding

- On power-up, game should remain in

IDLEuntil Start is pressed. Verify using State debug signal. - Provide an 8-bit seed and press Start — game should transition to

DISPLAY. Verify using State debug signal. - Using the same seed should yield the same sequence. Different seeds should generate different sequences (LFSR test).

Reset Behavior

- Press reset in any state — game should return to

IDLE, discarding current game state.- Test reset: before

IDLE, duringIDLE,DISPLAY,WAIT,CHECK

- Test reset: before

External hardware

| Component | Quantity | Notes |

|---|---|---|

| Push Buttons | 6 | Red, Blue, Green, Yellow, Start, Reset |

| LEDs | 4 | One for each color, with pull-down resistors |

| Raspberry Pi | 1 | Sends 8-bit seed to the chip and reads in a 2-bit State Debug Signal |

To match encoding the following outputs should be wired to these colour leds:

- uo[0] = red

- uo[1] = blue

- uo[2] = yellow

- uo[3] = green

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | input_0 | output_0 | bidir_0 |

| 1 | input_1 | output_1 | bidir_1 |

| 2 | input_2 | output_2 | bidir_2 |

| 3 | input_3 | output_3 | bidir_3 |

| 4 | input_4 | output_4 | bidir_4 |

| 5 | input_5 | output_5 | bidir_5 |

| 6 | input_6 | output_6 | bidir_6 |

| 7 | input_7 | output_7 | bidir_7 |