1006 Simple Cache Controller

1006 : Simple Cache Controller

- Author: TT12-01

- Description: A small direct-mapped cache memory controller

- GitHub repository

- Open in 3D viewer

- Clock: 1000000 Hz

How it works

This project implements a simple direct-mapped cache memory controller that manages data storage and retrieval for 4 cache blocks. The CPU sends an 8-bit address along with a read/write signal through input pins. On a write, the data is stored in the cache and marked dirty. On a read, if the address matches a valid cache block, data is returned from the cache to the output pins. If the block is not present, the controller simulates a cache miss by loading a placeholder value.

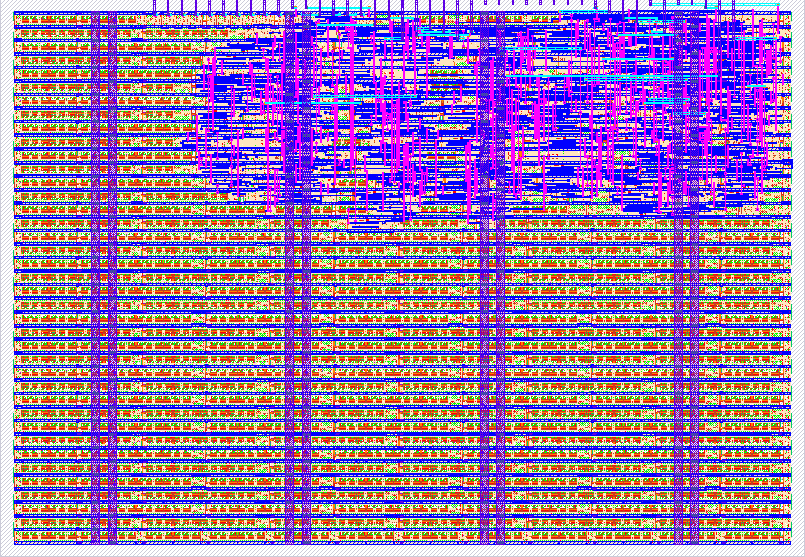

The design fits within Tiny Tapeout SkyWater 130nm process constraints with 8 input/output pins, handling cache logic and interfacing efficiently. The core cache runs synchronously with the injected clock and reset signals.

How to test

To test the design, drive the input pins (ui_in) with the address and read/write control bits. For example, set the MSB high to indicate a write operation and provide the lower address bits for caching. Then observe the output pins (uo_out) for read data results.

Simulation testbench and cocotb tests are included to verify basic cache operations like read hits, write hits, and read misses.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | Address bit 0 | Data output bit 0 | |

| 1 | Address bit 1 | Data output bit 1 | |

| 2 | Address bit 2 | Data output bit 2 | |

| 3 | Address bit 3 | Data output bit 3 | |

| 4 | Address bit 4 | Data output bit 4 | |

| 5 | Address bit 5 | Data output bit 5 | |

| 6 | Address bit 6 | Data output bit 6 | |

| 7 | Read/Write flag (MSB of address) | Data output bit 7 |