232 4-bit Array Multiplier

232 : 4-bit Array Multiplier

- Author: Minjae Kim, Jiawei Ding

- Description: 4-bit array multiplier using structural Verilog

- GitHub repository

- Open in 3D viewer

- Clock: 0 Hz

How it works

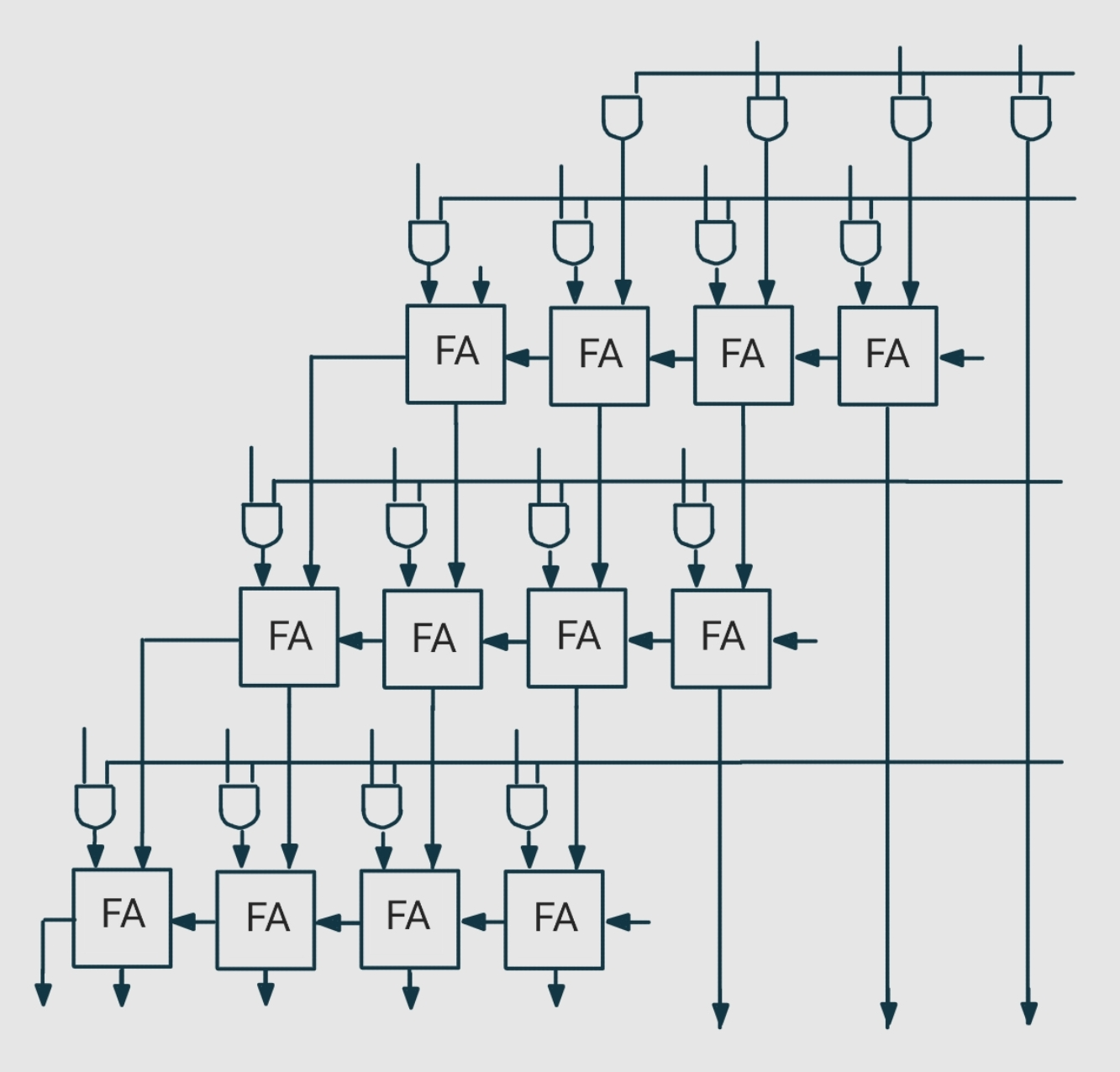

This project implements a 4-bit array multiplier using structural Verilog. It takes two 4-bit binary inputs (m and q) and computes their product, outputting the result as an 8-bit binary number. The multiplication is performed using an array multiplier architecture, which generates partial products for each bit of the inputs and sums them using a series of adders.

Partial products are calculated based on the bits of each 4-bit input. The summation of partial products is arranged in stages, and the final result is accumulated through these stages, producing an 8-bit result (uo_out[7:0]).

How to test

- Input Setup: Connect the first 4-bit input

mthroughui_in[3:0]and the second 4-bit inputqthroughuio_in[3:0]. - Observing Output: The 8-bit product of

mandqwill be output onuo_out[7:0]. - Clock and Reset: Although there are

clkandrst_nsignals in the design, they are not utilized in this version of the array multiplier, which operates as a combinational circuit.

Example Test Case

- Inputs: Set

mto4'b0011(decimal 3) andqto4'b0010(decimal 2). - Expected Output:

uo_outshould be8'b00000110(decimal 6).

Testing can be performed on a simulation platform (such as Verilog testbenches in ModelSim or other simulation tools) by assigning values to ui_in and uio_in and verifying the uo_out output.

External hardware

This project does not require any external hardware. All inputs and outputs are managed internally within the module, which can be tested in simulation environments or FPGA-based hardware setups.

Circuit Diagram

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | m[0] | ||

| 1 | m[1] | ||

| 2 | m[2] | ||

| 3 | m[3] | ||

| 4 | q[0] | ||

| 5 | q[1] | ||

| 6 | q[2] | ||

| 7 | q[3] |