199 4x4 Array Multiplier

199 : 4x4 Array Multiplier

- Author: Marisol and Shahran

- Description: 4x4 structural Array Multiplier

- GitHub repository

- Open in 3D viewer

- Clock: 0 Hz

How it works

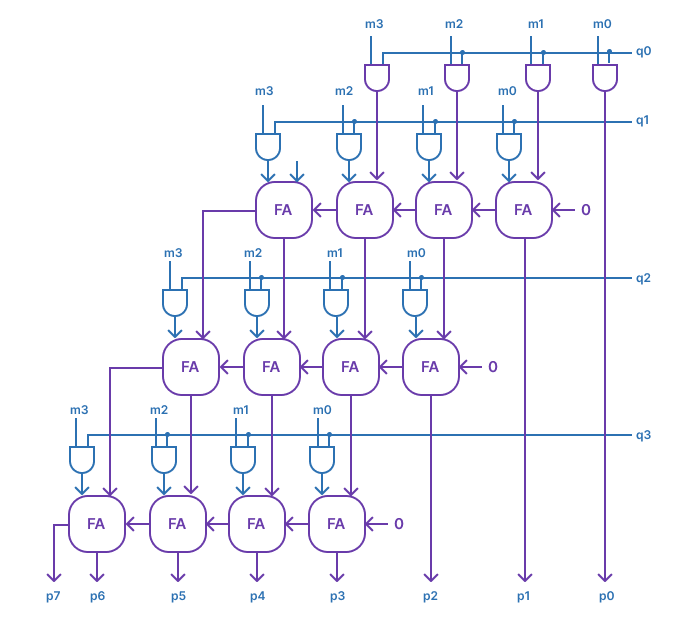

Our implementation of the multiplier took in two 4-inputs, m and q, and produced an 8-bit output, p, representing their product. We then genereated partial products by ANDing each bit of m with all bits of q and used a series of full adders, to sum these partial products. Each adder handled the addition of bits and carry-out/carry-in signals from the previous stage, ensuring proper alignment of the products.

How to test

We parse in an 8-bit value which is split into 2 4-bit values to generate m(bits 8 to 5), and q(bits 4 to 1). These two values are then multiplied to produce our product p.

External hardware

N/A

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | q[0] | p[0] | |

| 1 | q[1] | p[1] | |

| 2 | q[2] | p[2] | |

| 3 | q[3] | p[3] | |

| 4 | m[0] | p[4] | |

| 5 | m[1] | p[5] | |

| 6 | m[2] | p[6] | |

| 7 | m[3] | p[7] |