909 Pong

909 : Pong

- Author: Alex Segura

- Description: 2-player pong game

- GitHub repository

- Open in 3D viewer

- Clock: 25175000 Hz

{width=60%}

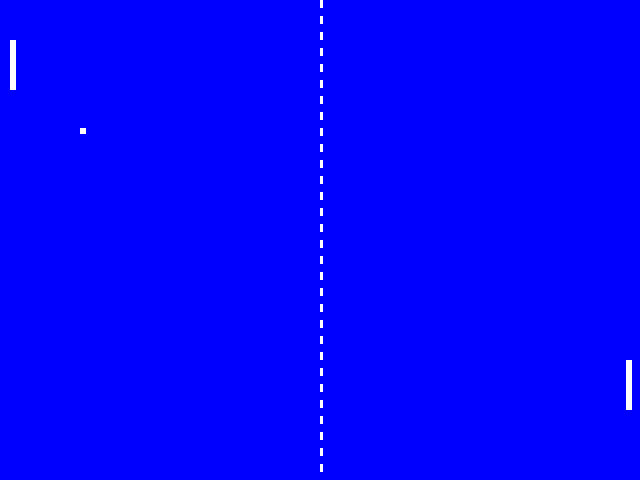

{width=60%}

How it works

The pixel clock drives a VGA sync generator that scans the screen. Logic in pong.v determines whether to draw a pixel.

At each vsync, collisions are detected and the state of the game is updated.

For the paddle controls, the game uses modified versions of the debounce and encoder logic from the course to generate the control signals.

How to test

Two vertical paddles and a ball should render at 640x480 resolution. A vertical "net" should be visible at the middle of the screen. Paddles should respond to the encoders. The ball should bounce from the top and bottom boundaries of the screen and should bounce off the paddles. The game should reset when the ball crosses beyond either paddle.

The verilog code can be run under verilator simulation:

cd src

make -B pong

./obj_dir/pong

SDL2 is a necessary dependency.

W and S control the left paddle. Up and down arrow keys control the right paddle.

External hardware

- Two rotary encoders, one for each paddle.

- TinyVGA Pmod or similar.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | Paddle 1 encoder A | R0 | |

| 1 | Paddle 1 encoder B | G0 | |

| 2 | Paddle 2 encoder A | B0 | |

| 3 | Paddle 2 encoder B | VSYNC | |

| 4 | R1 | ||

| 5 | G1 | ||

| 6 | B1 | ||

| 7 | HSYNC |