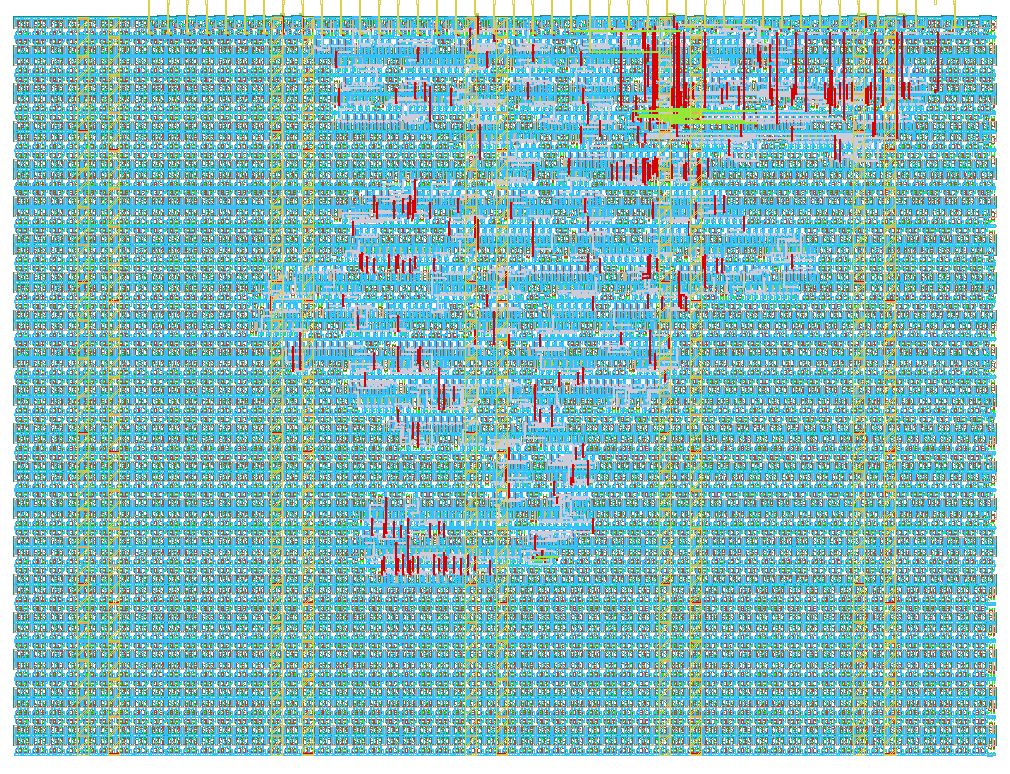

877 Verilog ring oscillator

877 : Verilog ring oscillator

- Author: algofoogle (Anton Maurovic)

- Description: Simple ring oscillator by instantiating a sky130 inv_2 inverter ring

- GitHub repository

- Open in 3D viewer

- Clock: 0 Hz

What is this?

Everyone has done a ring oscillator using inverter cells. Now it's my turn!

This simple example uses Verilog to instantiate a ring of (an odd number of) sky130_fd_sc_hd__inv_2 cells -- UPDATE: Actually, since this is targeting IHP instead, there is a polyfill that somebody else wrote to map sky130 cells to generic cells (that OpenLane will then map to IHP cells).

It produces its output on uo_out[0].

Assuming each inverter introduces a delay of ~70ps, and there are 1001 of them, then hopefully this will oscillate at ~14MHz?

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | osc_out | ||

| 1 | |||

| 2 | |||

| 3 | |||

| 4 | |||

| 5 | |||

| 6 | |||

| 7 |