516 Verilog ring oscillator V2

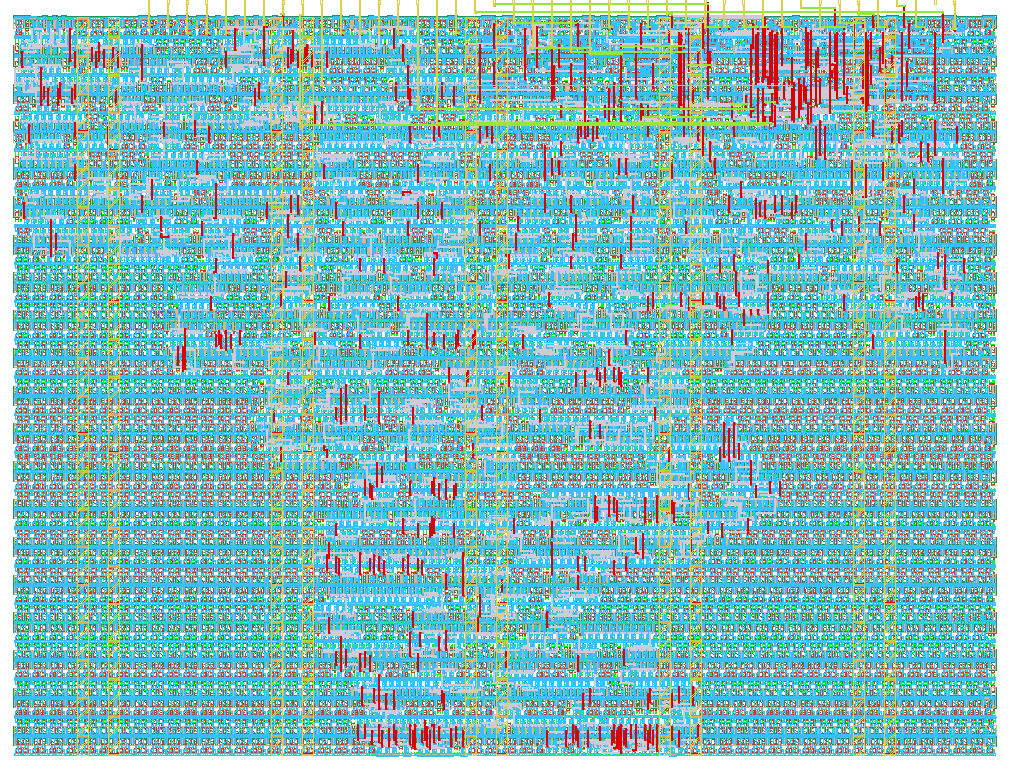

516 : Verilog ring oscillator V2

- Author: algofoogle (Anton Maurovic)

- Description: Multiple ring oscillators with simple PWM experiments

- GitHub repository

- Open in 3D viewer

- Clock: 0 Hz

Overview

For a quick-start guide just see the "How to test" heading below. I intend to have results collected in the TTIHP25a-ring-osc2 sheet of my "Anton's Tiny Tapeout silicon testing" Google Sheet.

There are 6 ring oscillators of various lengths in this design, ranging from 13 inverters up to 1001 inverters. 4 of them give their direct outputs. 4 also give their output divided by 16. 2 also drive PWM outputs at high frequency to see whether the output pins will filter them to "analog-like" waveforms, or whether instead the chip characteristics just kill the outputs.

This is implemented using the IHP SG13G2 open PDK and was fabricated on TTIHP25a, though it was originally intended for TT09.

Originally this project was submitted to TT09 (commit ee2feec). It was later rehardened for resubmission to TTIHP25a (wherein some minor changes were required).

See also: tt09-ring-osc and tt09-ring-osc3 for my other ring oscillator experiments on the same shuttle.

How to test

- Set

ui_into 0; this should configure all the PWM experiments to do nothing. - Probe

uo_out[3](ring_1001) with an oscilloscope: This is the raw output of the longest (1001-inverter) ring oscillator. - Probe through each of

uo_out[2:0]: Each step to a lower bit is another ring that is half the length (and hence should be double the frequency): 501 inverters (ring_501), then 251 inverters (ring_251), then 125 inverters (ring_125). - Probe

uo_out[4](c0_3): This isring_501divided by 16. - Probe

uo_out[5](c1_3): This isring_125divided by 16. - Probe

uo_out[6](c2_5): This is the much fasterring_25divided by 64. - Probe

uo_out[7](c3_5): This is the fastestring_13divided by 32 -- probably too fast (on the order of 120MHz?) - Probe

uio_out[7,6,1]: These are the PWM experiment outputs and all are expected to be at 0. - Probe

uio_out[7,6,1]while settingui_into each of:00100101: 25% duty PWM foruio_out[7]anduio_out[6], 12.5% duty foruio_out[1].01001010: 50% duty PWM foruio_out[7]anduio_out[6], 25% duty foruio_out[1].01101111: 75% duty PWM foruio_out[7]anduio_out[6], 37.5% duty foruio_out[1].10000000: 50% duty foruio_out[1].10100000: 62.5% duty foruio_out[1].11000000: 75%11100000: 87.5%

The hope is that the PWM outputs are at a high enough frequency that the duty cycle will be somewhat filtered to give an analog-like output, though it's likely the chip's mux and other characteristics along the way (including the pad drivers) will just lead to outputs that are mostly noisy.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | pwm2_in[0] | ring_125 | dummy |

| 1 | pwm2_in[1] | ring_251 | pwm3a_out |

| 2 | pwm3_in[0] | ring_501 | |

| 3 | pwm3_in[1] | ring_1001 | |

| 4 | c0_3 | ||

| 5 | pwm3a_in[0] | c1_3 | |

| 6 | pwm3a_in[1] | c2_5 | pwm2_out |

| 7 | pwm3a_in[2] | c3_5 | pwm3_out |