2 Verilog ring oscillator V3

2 : Verilog ring oscillator V3

- Author: algofoogle (Anton Maurovic)

- Description: TTIHP25a resubmission of TT09 ring oscillator with externally-selectable length

- GitHub repository

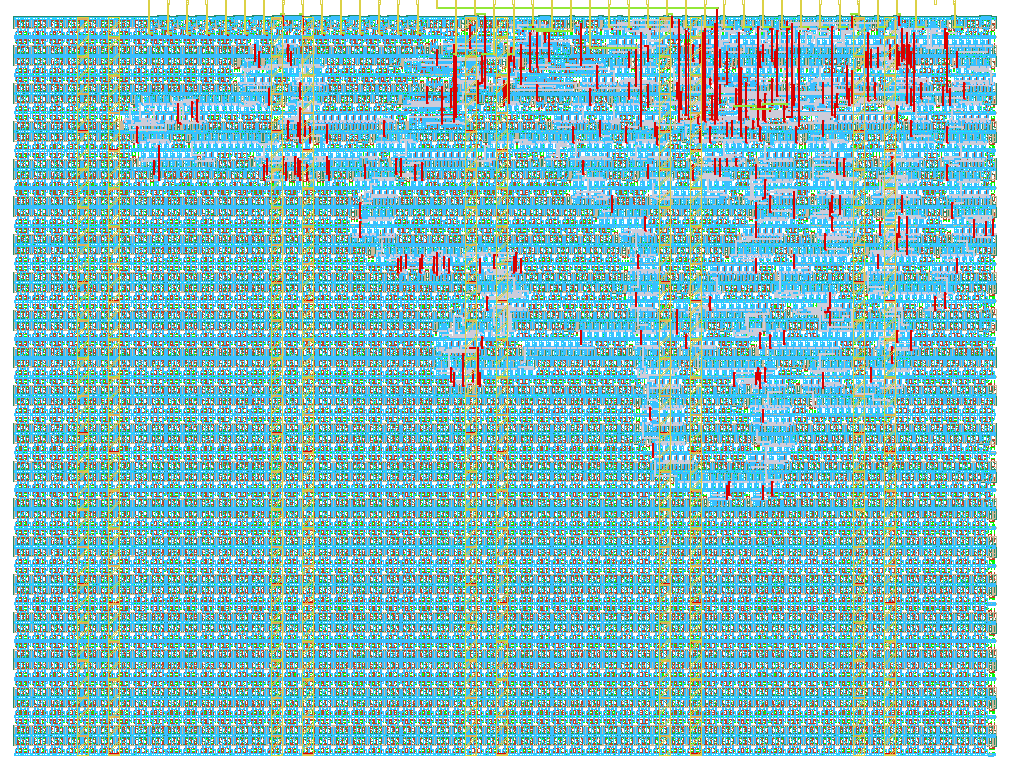

- Open in 3D viewer

- Clock: 0 Hz

Overview

For a quick-start guide just see the "How to test" heading below. I intend to have results collected in the TTIHP25a-ring-osc3 sheet of my "Anton's Tiny Tapeout silicon testing" Google Sheet.

This is a ring oscillator of configurable length, allowing selection from 0 (shortest, 11 inverters) to 7 (longest, 1001 inverters), with both raw oscillator output and counter-divided outputs.

It is implemented using the IHP SG13G2 open PDK and was fabricated on TTIHP25a, though it was originally intended for TT09.

Originally this project was submitted to TT09 (commit 5786e93). It was later rehardened for resubmission to TTIHP25a (wherein some minor changes were required).

See also: tt09-ring-osc and tt09-ring-osc2 for my other ring oscillator experiments on the same shuttle.

How does it work?

Verilog instantiates a chain of 1001 inverters (made up of smaller chain segments). ui_in[2:0] ("tap[2:0]") selects one of 8 tap points to loop back and hence make a ring oscillator of configurable length.

The output of the ring oscillator is presented on uo_out[0], but it also drives a 7-bit counter which is presented on uo_out[7:1].

At power-up, the state of the ring is expected to be random/chaotic. The ena signal gates the loopback, i.e. while ena is low, the chain should stabilise itself after a while (~40ns est.) but it won't loop back and hence won't oscillate. This is good, because designs are not power-gated on TTIHP25a: since the design is powered from the get-go, with ena initially low the chain will stabilise, and then as ena goes high (i.e. as the design is selected/enabled) the ring should be able to start oscillating cleanly. At least, this is what it looked like in simulation.

How to test

- Attach an oscilloscope to

uo_out[0](raw oscillator output) anduo_out[7](7th stage of a counter, i.e. divide-by-128). - Set

ui_in=0-- this is the shortest ring (11 inverters), hence the fastest. - Activate (i.e. select) the design.

uo_out[0]will probably be attenuated to nothing, but hopefullyuo_out[7]will show a clean oscillation (and lower bits will hopefully show it at higher frequencies) -- though with the shortest ring even the div-128 frequency onuo_out[7]could be quite high (28~65MHz?) and may even be erratic if the counter's lower bits are being clocked too fast?- Try setting

ui_in=7-- this is the longest ring (1001 inverters). - Hopefully observe

uo_out[0]is now slow enough to be measured, anduo_out[7]is a 128th of that frequency (and probably about 91 times slower than it was in step 4).

Setting tap (ui_in[2:0]) to one of the following values sets the ring oscillator to the respective length:

- 11 inverters

- 21 inverters

- 31 inverters

- 41 inverters

- 51 inverters

- 101 inverters

- 301 inverters

- 1001 inverters

Note that changing ui_in while the design is active might introduce a repeating glitch. Ideally, ui_in should assert the desired value (0..7) before the design is selected/activated, but I think the TT Commander by default always sets ui_in to 0 when selecting a design. If that's the case, setting ui_in and deactivating/activating the design might need to be done manually in the Commander with MicroPython code.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | tap[0] | out[0] | |

| 1 | tap[1] | out[1] | |

| 2 | tap[2] | out[2] | |

| 3 | out[3] | ||

| 4 | out[4] | ||

| 5 | out[5] | ||

| 6 | out[6] | ||

| 7 | out[7] |