387 7-segment with LFSR

387 : 7-segment with LFSR

- Author: Jun-ichi OKAMURA

- Description: TEST 7-segment/LFSR

- GitHub repository

- Open in 3D viewer

- Clock: 50000000 Hz

How it works

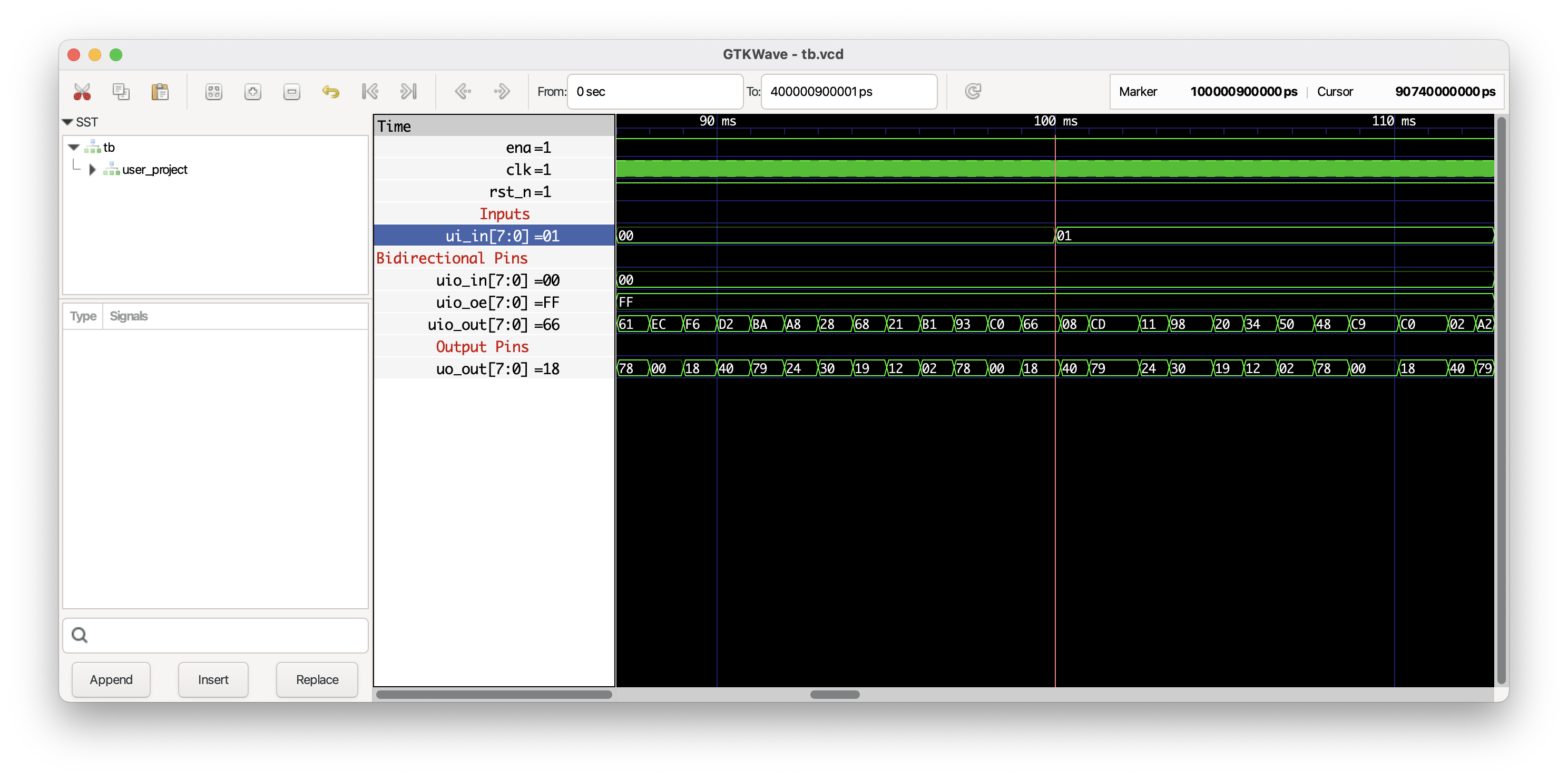

This design uses a set of registers to divide the clock and combinational logic to convert binary values into decimal for display.

- Inputs[0]: Selects between a fixed period or a pseudo-random period for counting up the seven-segment display.

- Inputs[1]: Chooses between displaying either a hexadecimal sequence (“0” to “F”) or the text ”-OPENSUSI-AISol-” on the display.

- Bidirectional Outputs: The bottom 8 bits of a 24-bit counter are placed on the bidirectional outputs.

Fixed Period Mode:

- The internal 16-bit compare register is set to 10,000.

- This results in the display incrementing by one each second in case the CLK input is 10KHz.

Pseudo-Random Period Mode:

- If Input[0] is set to 1, an 8-bit pseudo-random value is used as bits 6 to 12 of the 16-bit compare register, introducing variation in the counting period.

How to test

After reset, the counter will increment by one every second, assuming a 10MHz input clock.

You can experiment by modifying Inputs[1:0] to:

- Change the display characters

- Adjust the pseudo-random sequence of periodic speed

External hardware

Only TT-EVB.

Note

This is the first test project designed by “jun1okamura”, supported by OpenSUSI (non-profit) and AIST Solutions inc. in Japan.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | sel0 | segment a | counter bit 0 |

| 1 | sel1 | segment b | counter bit 1 |

| 2 | compare bit 13 | segment c | counter bit 2 |

| 3 | compare bit 14 | segment d | counter bit 3 |

| 4 | compare bit 15 | segment e | counter bit 4 |

| 5 | compare bit 16 | segment f | counter bit 5 |

| 6 | compare bit 17 | segment g | counter bit 6 |

| 7 | compare bit 18 | dot | counter bit 7 |