590 Divided Ring Oscillator

590 : Divided Ring Oscillator

- Author: Ignatius Bezzam, Dhandeep Challagundla, Jarnail Sanghera, Russell Kim

- Description: Ring Oscillator

- GitHub repository

- Open in 3D viewer

- Clock: 10000000 Hz

- Feedback: 🔴 1

How it works

A ring oscillator working in the GHz range is divided to give an observable output frequency in the 20 MHz range.

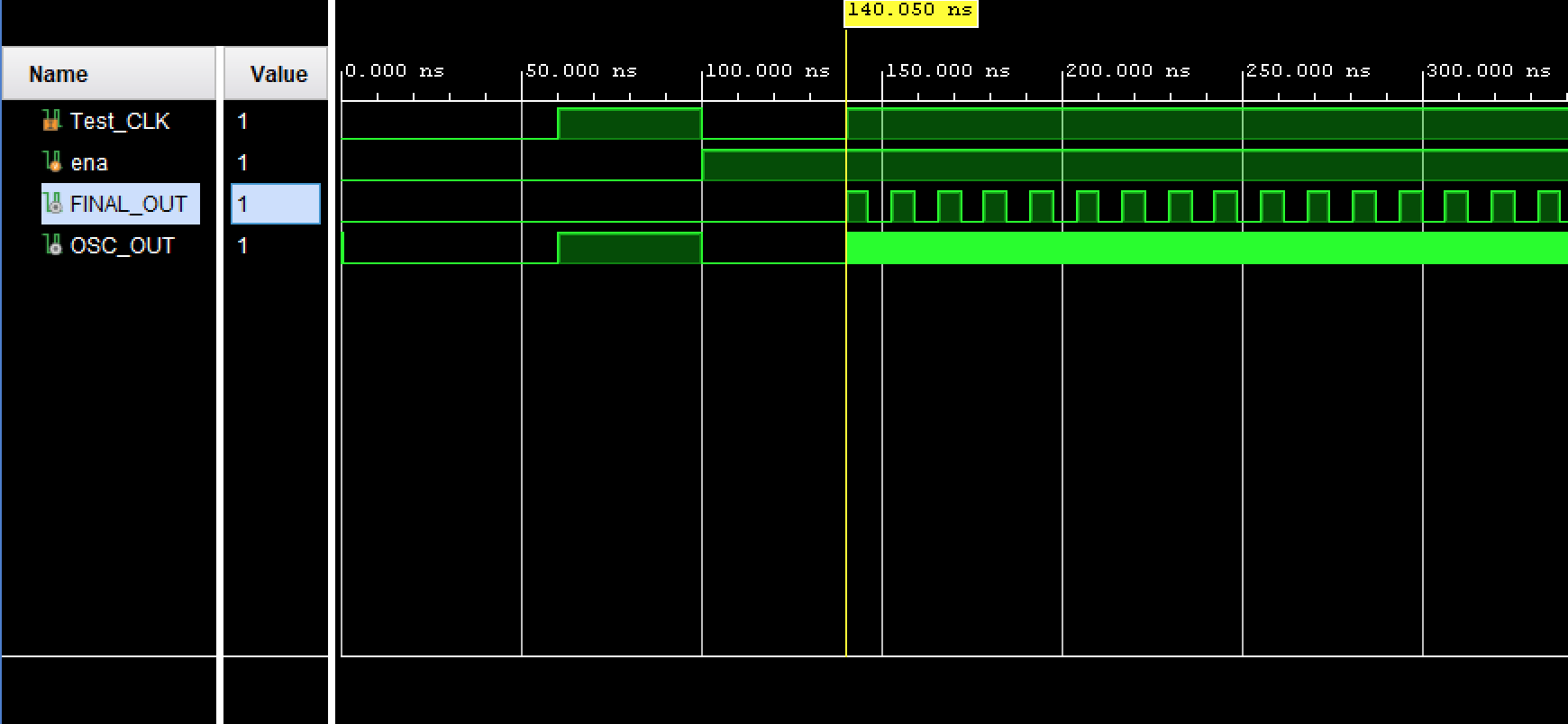

Top-Level Complete Mixed-Signal Functionality Verification in Verilog

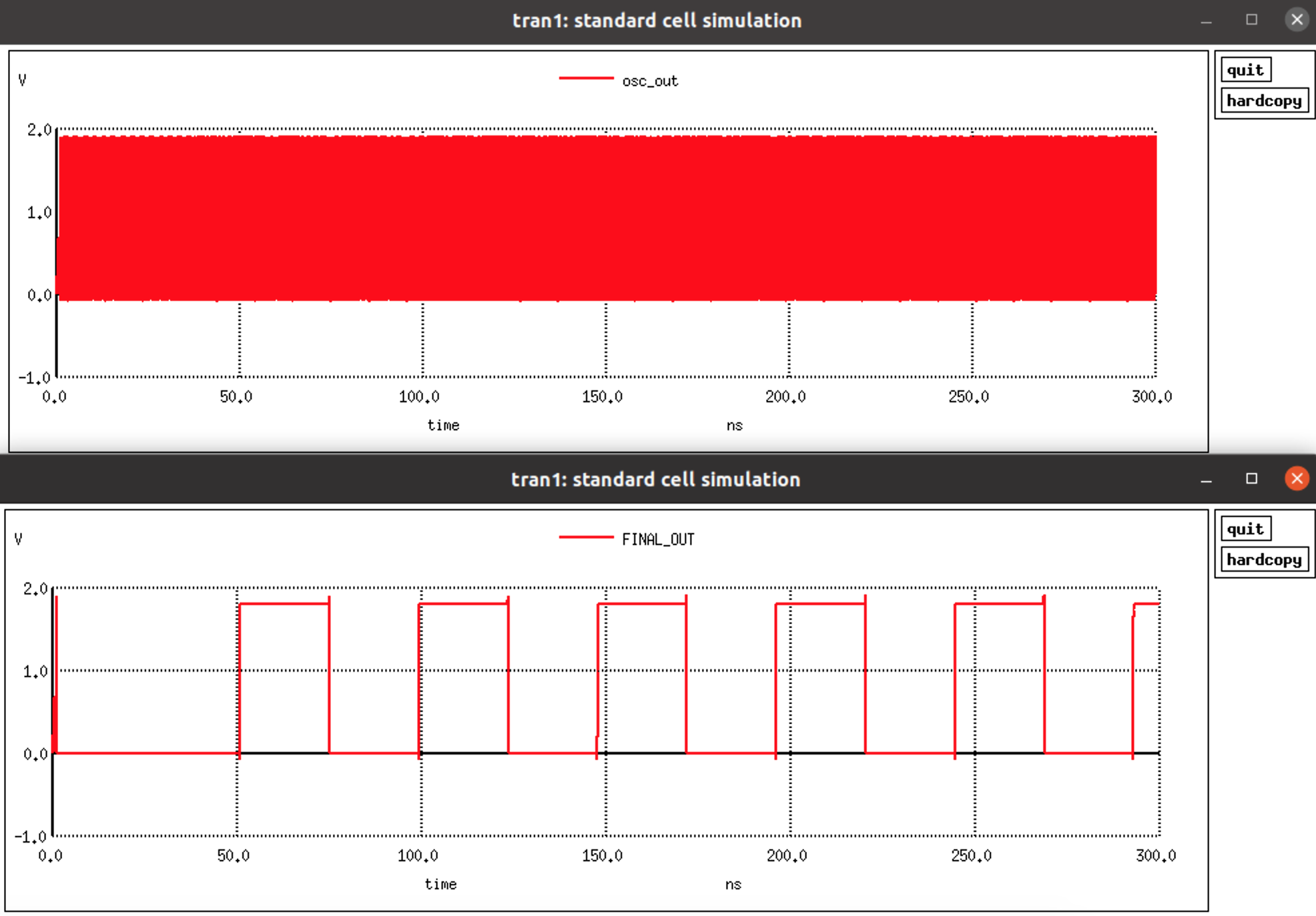

PEX Sims Verifying Performance

How to test

A supply current of 1-2 mA when enable is high indicates that the ring oscillator is functional. The final output can be observed in the 20 MHz range. Test/debug mode verifies the divider functionality at low frequency. The ring oscillator can be disabled by on-chip signals (ena = low).

External hardware

Oscilloscope (100 MHz), power supply, function generator (10 MHz, digital).

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | tst_clk | final_out | n1 |

| 1 | osc_out | n3 | |

| 2 | ena | ||

| 3 | clk | ||

| 4 | rst_n | ||

| 5 | n2_buf | ||

| 6 | n4_buf | ||

| 7 |

User feedback

- smunaut: No output can be observed. Toggling the enable pin shows current increase of about 100 uA but none of the output toggle. The verilog also shows that some of the debug / internal outputs were routed to uio_out but uio_oe is fixed to 0 so those pins are configured as inputs and can't be observed.