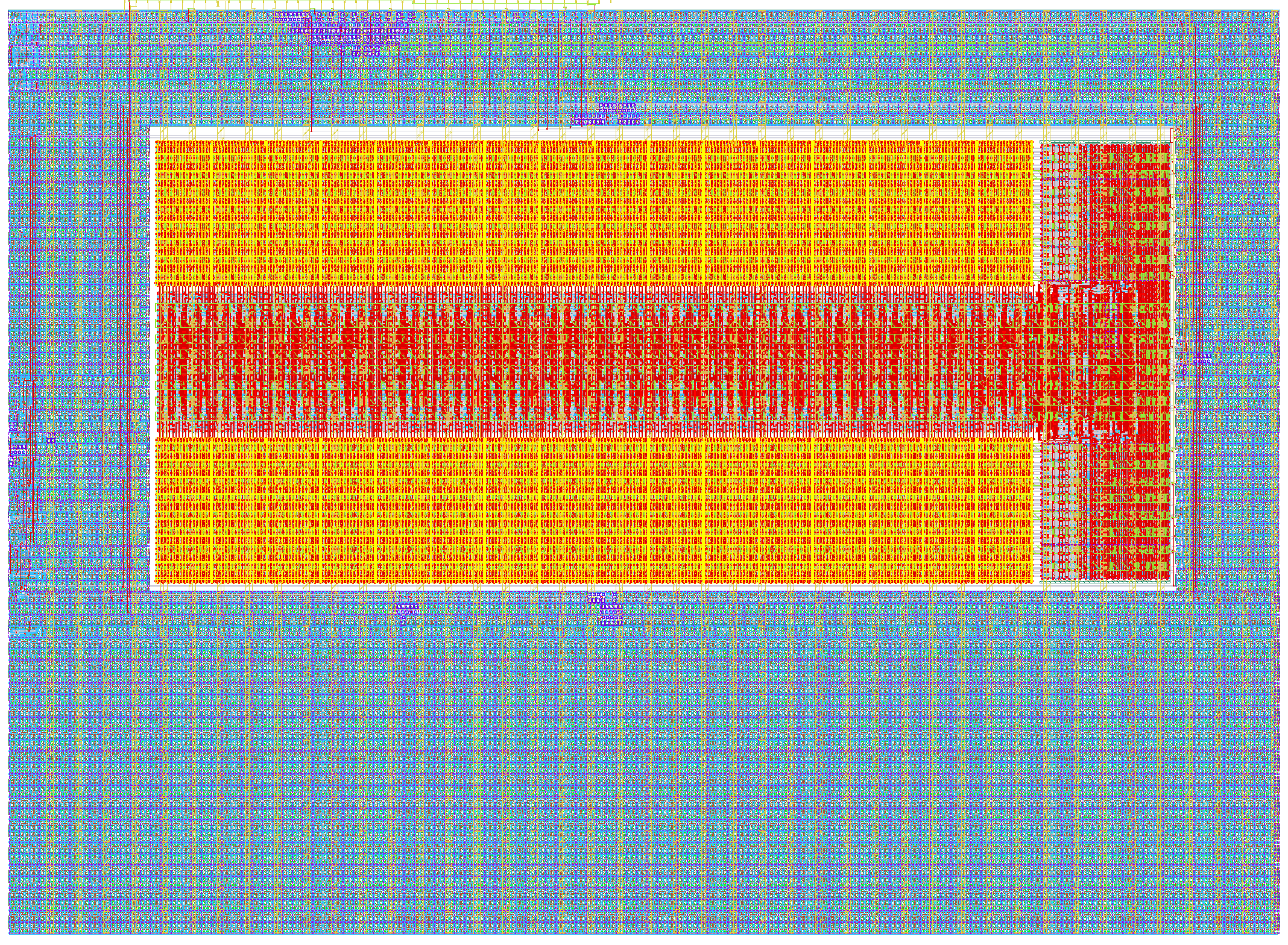

39 SRAM (1024x8) test

39 : SRAM (1024x8) test

- Author: Uri Shaked

- Description: Tests the foundry provided SRAM macro

- GitHub repository

- Open in 3D viewer

- Clock: 0 Hz

- Feedback: ✅ 1

How it works

This is a 1 kbyte SRAM controller module. It allows reading or writing a single byte at a time.

There are 10 address lines, 8 data lines, and 1 write enable line.

To read a byte, set the write enable line (wen) to 0, and the data lines (dout[7:0]) will be set to the value of the byte at the address specified by the address lines (addr[5:0]).

To write a byte, set the write enable line (wen) to 1, and set the data lines (din[7:0]) to the desired value. Writing is only possible when the bank_sel line is 0.

The lower 6 address bits (addr[5:0]) are exposed as input pins.

The upper 4 address lines are stored in the address_bank register. To change the upper address bits, set the bank_sel line to 1, and set the data lines (addr[9:6] / uio[3:0]) to the desired value.

How to test

- Set addr[5:0] to the desired address, set din[7:0] to the desired value, set wen to 1, and set bank_sel to 0, then pulse the clock line. The value at the specified address should be updated to the value of din[7:0].

- Set addr[5:0] to the desired address, set wen to 0, and set bank_sel to 0, then pulse the clock line. The value at the specified address should be output on dout[7:0].

- Set addr[9:6] to the desired value, set bank_sel to 1, then pulse the clock line. The upper address bits should be updated to the value of addr[9:6].

External hardware

None

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | addr[0] | dout[0] | din[0]/addr[6] |

| 1 | addr[1] | dout[1] | din[1]/addr[7] |

| 2 | addr[2] | dout[2] | din[2]/addr[8] |

| 3 | addr[3] | dout[3] | din[3]/addr[9] |

| 4 | addr[4] | dout[4] | din[4] |

| 5 | addr[5] | dout[5] | din[5] |

| 6 | bank_sel | dout[6] | din[6] |

| 7 | wen | dout[7] | din[7] |

User feedback

- mattvenn: Tested a few addresses with all values, and then all addresses with 0x00, 0xAA and 0xFF. Then random values at random addresses for 2M cycles.