171 Gray scale and Sobel filter

171 : Gray scale and Sobel filter

- Author: Diana Natali Maldonado Ramirez

- Description: Grayscale and Sobel filter.

- GitHub repository

- Open in 3D viewer

- Clock: 10000000 Hz

How it works

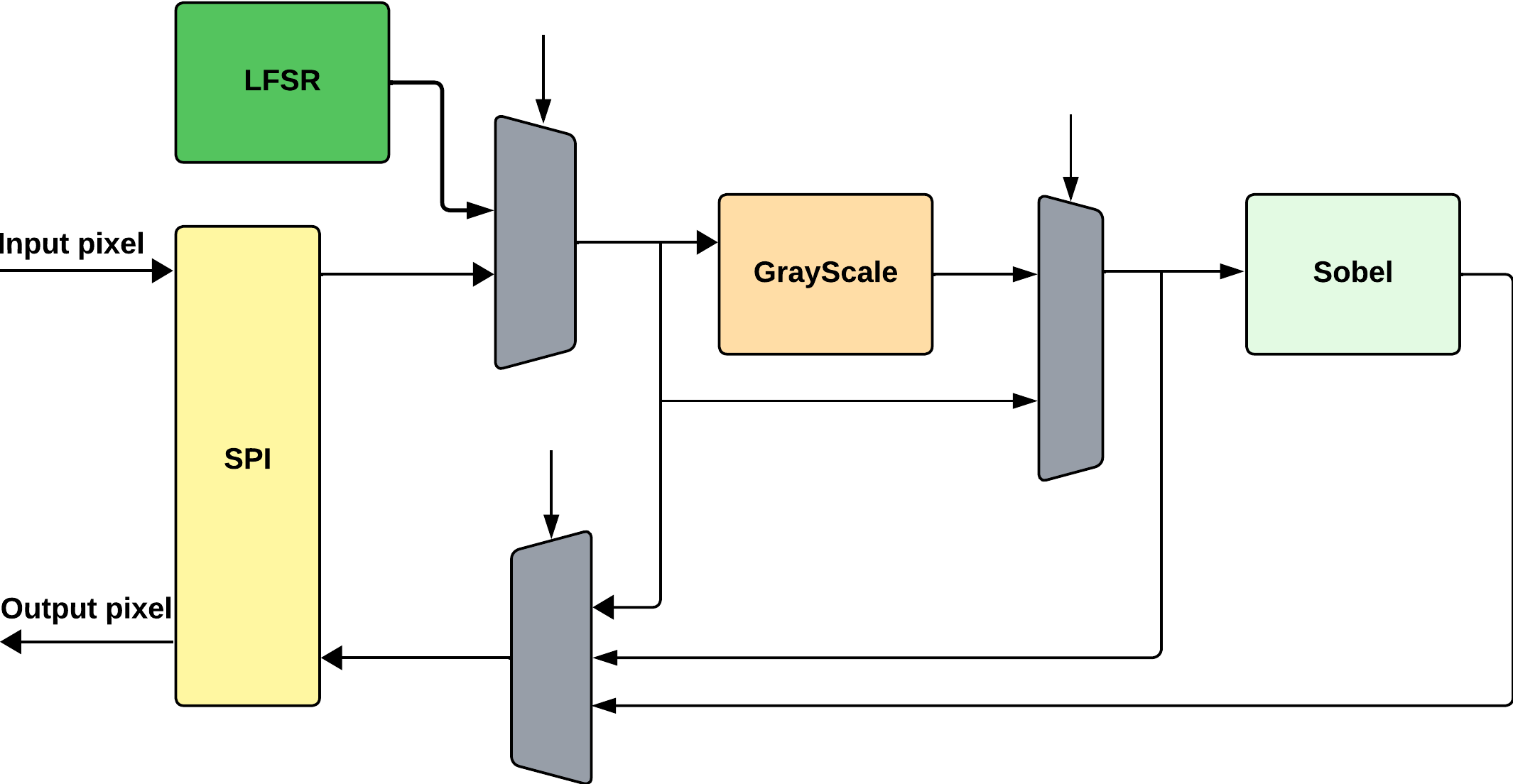

This project performs grayscale conversion and Sobel filtering with the aim of detecting edges in an image.

Below is a block diagram of the implementation:

How to test

It is necessary for the pixels to be sent via an SPI protocol; for this purpose, the input ui_in[2:0] is designated as follows:

ui_in[0]→ SPI Clockui_in[1]→ Chip Selectui_in[2]→ Input Pixel

As shown in the previous image, there are some processing options:

- Bypass → Returns the input pixel unprocessed.

- Grayscale → Returns the pixel converted to grayscale, so it is recommended that the input pixel be RGB.

- Sobel → Returns the edge detection corresponding to the input pixel, so it is recommended that the input pixel be grayscale.

- Grayscale + Sobel → Returns the edge detection of the input pixel by performing both grayscale processing and the Sobel filter, so it is recommended that the input pixel be RGB.

To select one of the processing options, the input ui_in[4:3] is designated as follows:

ui_in[4:3]= 00 → Grayscale + Sobelui_in[4:3]= 01 → Sobelui_in[4:3]= 10 → Grayscaleui_in[4:3]= 11 → Bypass

To perform the Sobel filter processing, it must be enabled according to the selected processing. This can be enabled or disabled as needed through the input ui_in[5], where 1 enables and 0 disables.

The result of the processing corresponds to the output uo_out[0].

There is also a functionality for the input to the different processing options to come from an internal LFSR block; for this purpose, the pins uio_in[3:2] are dedicated for input.

External hardware

Any device that allows sending and receiving data via an SPI protocol, like a Raspberry Pi.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | spi_sck_i | spi_sdo_o | LFSR_enable_i |

| 1 | spi_cs_i | lfsr_done | seed_stop_i |

| 2 | spi_sdi_i | ena | lfsr_en_i |

| 3 | select_process_i[0] | output_px[0] | |

| 4 | select_process_i[1] | output_px[1] | |

| 5 | start_sobel_i | output_px[2] | |

| 6 | output_px[3] | ||

| 7 | output_px[4] |