204 integer to posit converter and adder

204 : integer to posit converter and adder

- Author: A. Fasolino, G.D. Licciardo, A. Torino, F. Del Prete, C. Parrella

- Description: Our module executes a fixed to posit conversion and an addition

- GitHub repository

- Open in 3D viewer

- Clock: 30000000 Hz

How it works

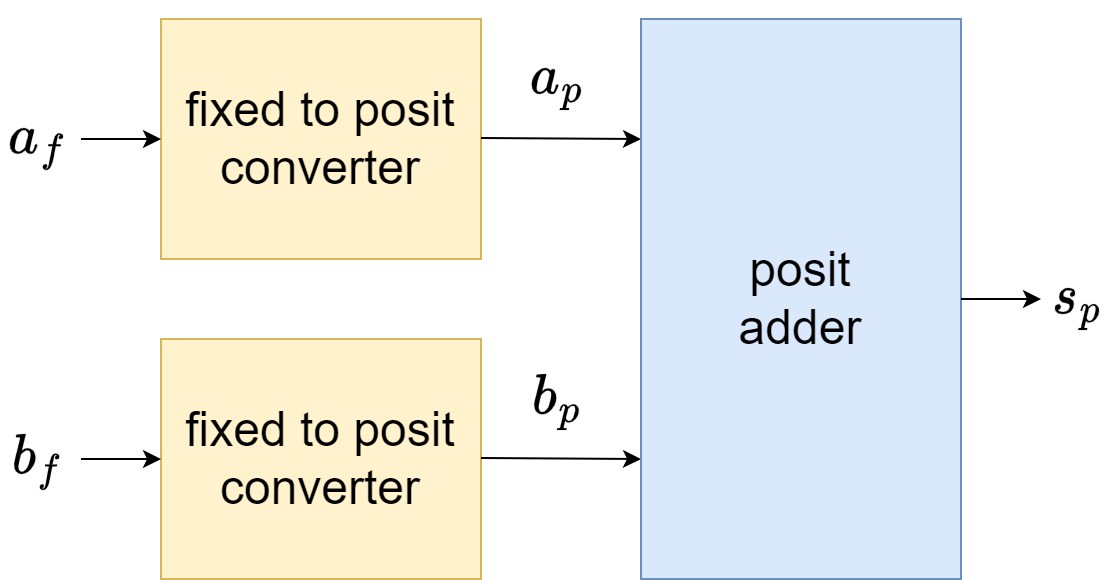

The module (Fig. 1) is fed by two fixed-point numbers, namely af and bf, coverts them into the posit arithmetic [1] format (ap and bp) and sums them to produce a posit output (sp).

It is made of two units:

- 16-bit 2's complement fixed-point 0.15 coded to 16-bit standard posit (16,1) converter, namely fixed to posit converter,

- posit adder, that executes the addition of posit numbers according to the posit standard.

The conversion is operated as described in [1], leveraging a leading zero counter [2] and some glue logic.

The addition leverages the architecture presented in [3].

How to test

Provide two fixed-point input data and they will be added in posit arithmetic.

References

[1] J. Gustafson. "Posit arithmetic." Mathematica Notebook describing the posit number system, 2017.

[2] Milenković, Nebojša & Stankovic, Vladimir & Milić, Miljana. (2015). Modular Design Of Fast Leading Zeros Counting Circuit. Journal of Electrical Engineering. 66. 329-333. 10.2478/jee-2015-0054.

[3] R. Murillo, A. A. Del Barrio and G. Botella, "Customized Posit Adders and Multipliers using the FloPoCo Core Generator," 2020 IEEE International Symposium on Circuits and Systems (ISCAS), 2020, pp. 1-5, doi: 10.1109/ISCAS45731.2020.9180771.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | data input | addition result | data valid |

| 1 | data input | addition result | alu valid |

| 2 | data input | addition result | read data valid |

| 3 | data input | addition result | read data ready |

| 4 | data input | addition result | |

| 5 | data input | addition result | |

| 6 | data input | addition result | |

| 7 | data input | addition result |