244 Balanced Ternary Calculator

244 : Balanced Ternary Calculator

- Author: Steven Bos

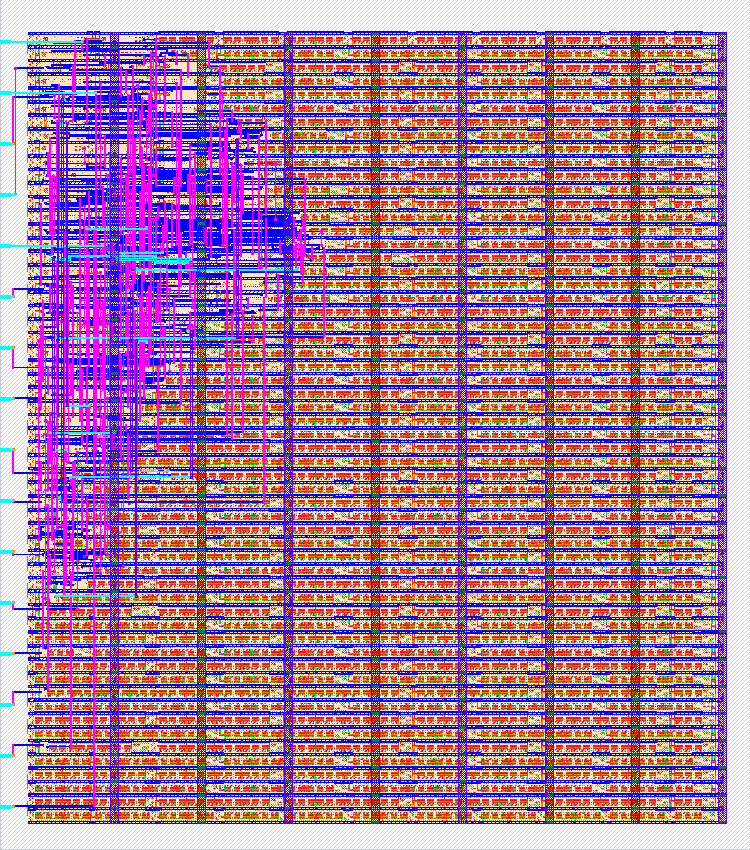

- Description: A balanced ternary calculator allowing multiplication, addition and subtraction with negative numbers in binary encoded ternary

- GitHub repository

- Open in 3D viewer

- Clock: 0 Hz

How it works

2DO

How to test

2DO

External hardware

none

IO

| # | Input | Output |

|---|---|---|

| 0 | x1H | s3H |

| 1 | x1L | s3L |

| 2 | x0H | s2H |

| 3 | x0L | s2L |

| 4 | Y1H | s1H |

| 5 | y1L | s1L |

| 6 | y0H | s0H |

| 7 | y0L (reused as function selector, eg add/subtract or multiply) | s0L |