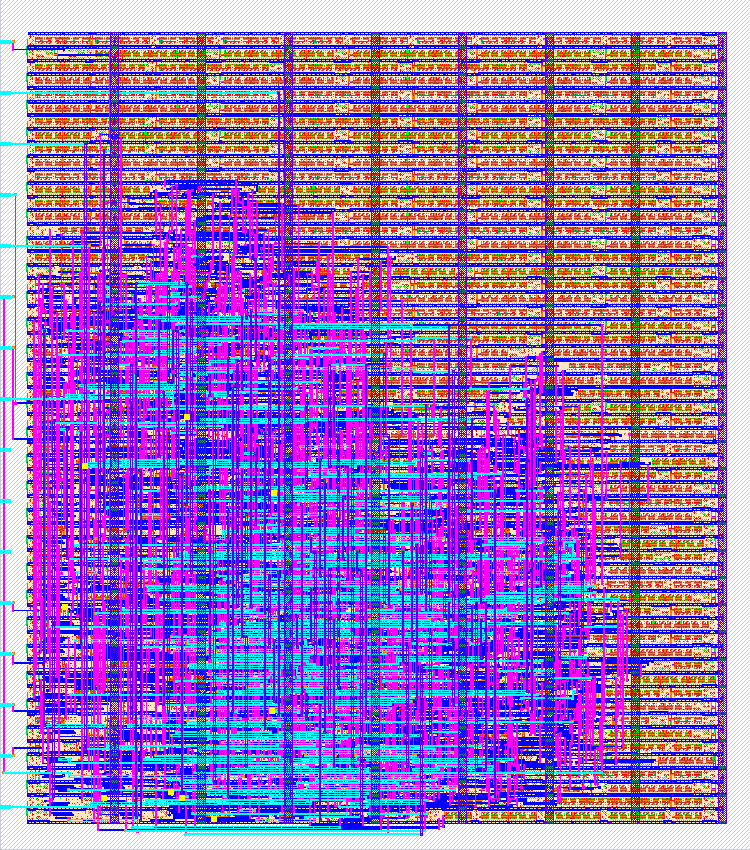

52 Neptune guitar tuner (proportional window)

52 : Neptune guitar tuner (proportional window)

- Author: Pat Deegan

- Description: It's a guitar tuner! and so much more... (TODO)

- GitHub repository

- Open in 3D viewer

- Clock: 1000 Hz

How it works

Uses a set of registers to divide the clock, and then some combinational logic to convert from binary to decimal for the display.

Puts a slower square wave output on output 7.

How to test

After reset, the counter should increase by one every second.

External hardware

The analog input signal must be massaged into clean digital. See the Neptune project for details https://github.com/psychogenic/neptune

IO

| # | Input | Output |

|---|---|---|

| 0 | clock | segment a |

| 1 | reset | segment b |

| 2 | clock config A | segment c |

| 3 | clock config B | segment d |

| 4 | measured frequency input pulses | segment e |

| 5 | segment f | |

| 6 | segment g | |

| 7 | display select |