63 CNS002 (TT02-Test 2)

63 : CNS002 (TT02-Test 2)

- Author: Bryan Bonilla Garay, Devin Alvarez, Ishaan Singh, Yu Feng Zhou, and N. Sertac Artan

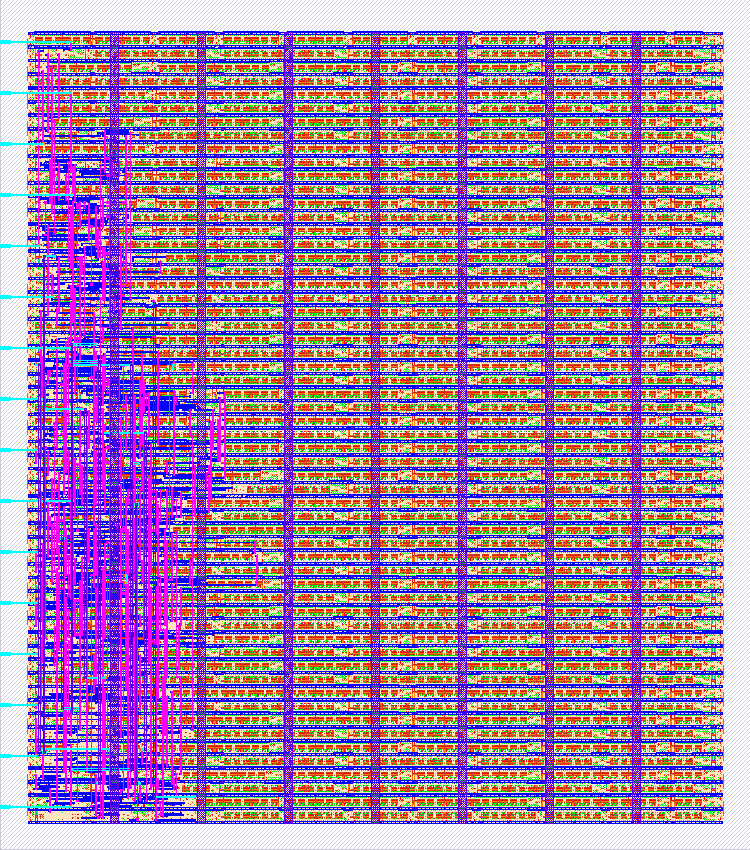

- Description: First test run of CNS Lab (second design)

- GitHub repository

- Open in 3D viewer

- Clock: 0 Hz

How it works

Apply inputs, get outputs

How to test

Wokvi

External hardware

None

IO

| # | Input | Output |

|---|---|---|

| 0 | clock | segment a |

| 1 | reset | segment b |

| 2 | segment c | |

| 3 | segment d | |

| 4 | segment e | |

| 5 | segment f | |

| 6 | segment g | |

| 7 |