526 AICD Playground

526 : AICD Playground

- Author: Leo Moser

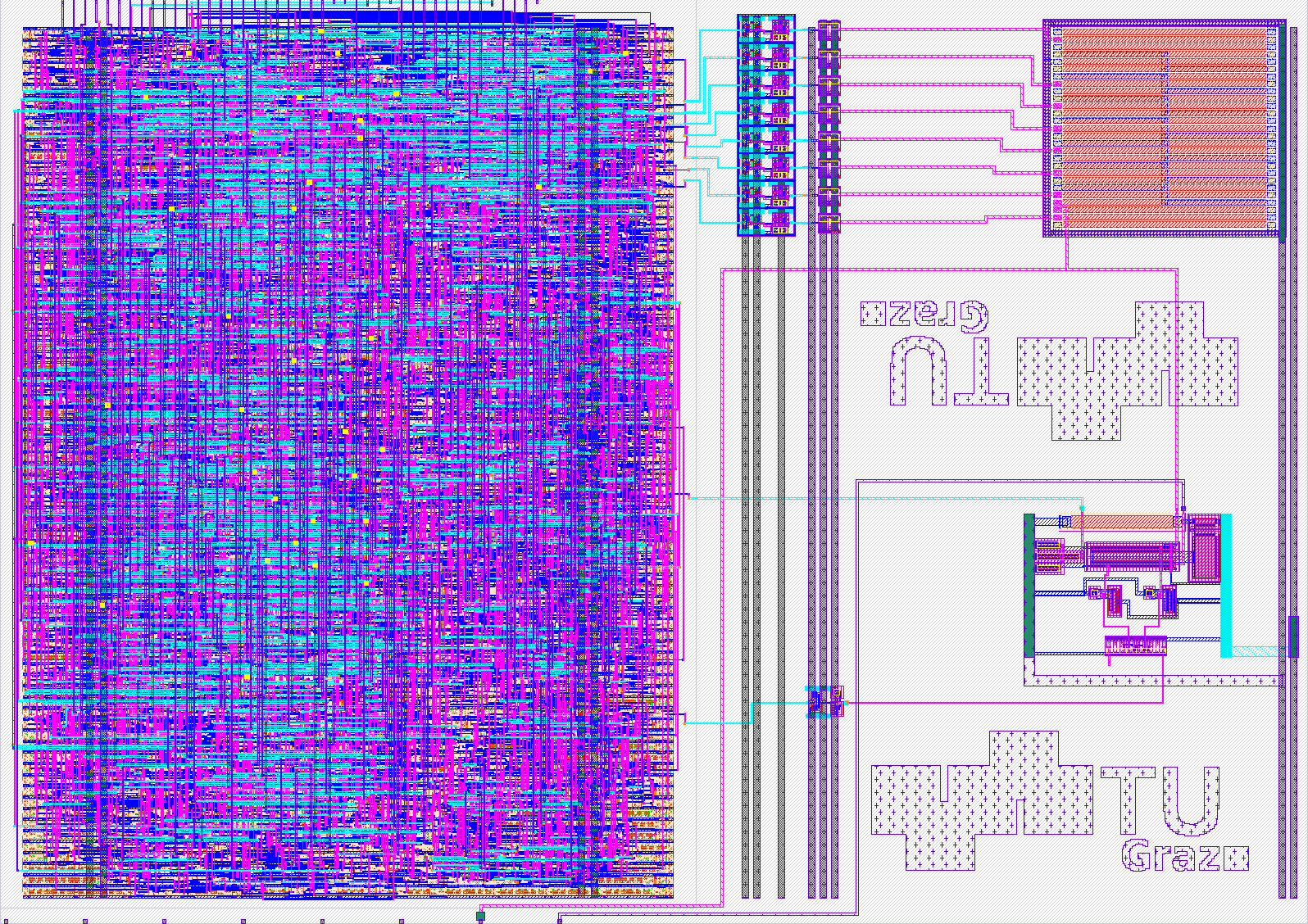

- Description: A mixed-signal test project for the analog IC design course at Graz University of Technology.

- GitHub repository

- Open in 3D viewer

- Clock: 1000000 Hz

How it works

AICD Playground is a mixed-signal test project for the analog IC design course at Graz University of Technology.

It integrates a digital 8-bit controller with several analog IPs such as up/down-levelshifters, an R2R-DAC and a comparator. The IPs are connected in a way that a simple SAR-ADC is formed.

How to test

To initialize the memory, you need to set the mode pin to high. Now data can be send via the SPI interface, which is then written into the memory. After a rising edge of mode, the address points to zero and is incremented with each SPI transaction. Send 64 bytes to initialize the whole memory.

Next, set mode to low. The CPU starts executing the program. Depending on the program that is loaded, an analog voltage is applied to ua[1] via the R2R-DAC. This voltage is compared with the voltage at ua[0] and the result can be read by the CPU. In this way, a simple SAR-ADC can be programmed.

External hardware

No external hardware necessary.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | port_i[0] | port_o[0] | CS |

| 1 | port_i[1] | port_o[1] | MOSI |

| 2 | port_i[2] | port_o[2] | MISO |

| 3 | port_i[3] | port_o[3] | SCK |

| 4 | port_i[4] | port_o[4] | mode |

| 5 | port_i[5] | port_o[5] | debug_i |

| 6 | port_i[6] | port_o[6] | debug_o[0] |

| 7 | port_i[7] | port_o[7] | debug_o[1] |

Analog pins

ua | PCB Pin | Internal index | Description |

|---|---|---|---|

| 0 | B5 | 11 | adc_in |

| 1 | B0 | 6 | dac_out |